Tin tức

DAC khám phá vai trò của AI và ML trên các thị trường

Trung tâm Moscone, San Francisco, sẽ tổ chức DAC 25-28 / 6

OneSpin Solutions và Austemper Design Systems sẽ làm nổi bật các công cụ để xác minh an toàn chức năng. Austemper sẽ tập trung vào phát triển hệ thống quan trọng, với bộ công cụ KaleidoScope hỗ trợ thiết kế tương tự để lan truyền lỗi tín hiệu hỗn hợp đồng thời. Bộ công cụ tự động có khả năng phân tích, tổng hợp và xác minh an toàn cho các ứng dụng hướng đến chứng nhận. Nó được sử dụng cho các thiết kế ô tô quy mô lớn trong ADAS và lái xe tự trị. Mô phỏng lỗi đồng thời bao gồm các mô phỏng được khuyến nghị bởi ISO 26262 để tuân thủ các yêu cầu ASIL.

Công ty gần đây đã hợp tác với OneSpin Solutions để áp dụng phương pháp hỗ trợ công cụ cho các ứng dụng an toàn chức năng, kết hợp quy trình thiết kế và xác minh, sẽ được trình bày tại gian hàng OneSpin. Các cơ chế an toàn phần cứng được chèn vào các thiết kế chip và các công cụ OneSpin Solutions, chính thức xác minh logic an toàn phần cứng. Kiểm tra tương đương đảm bảo rằng logic an toàn được chèn không ảnh hưởng đến chức năng thông thường và phân tích phát hiện lỗi xác minh rằng các cơ chế an toàn thực hiện đúng trong trường hợp có lỗi ngẫu nhiên.

OneSpin cũng đang quảng bá bộ công cụ Trình độ công cụ của mình, sau khi T verificationV SÜD xác minh các quy trình phát triển công cụ của mình. Bộ công cụ ban đầu có sẵn cho công cụ EDA 360 360 của công ty, một công cụ kiểm tra tương đương tuần tự tự động nhằm ngăn chặn các luồng thiết kế của FPGA đưa ra các lỗi thực hiện. Bộ sản phẩm được chứng nhận ISO 26262, IEC 61508 và EN 50128.

Hiểu biết sâu sắc về đồ họa

Vẫn với thiết kế đồ họa, Plunify đã hợp tác với Xilinx để cung cấp bộ thiết kế Vivado trên đám mây, thông qua nền tảng Plunify Cloud. Các nhà thiết kế phải trả ít nhất 50c để biên dịch dự án Vivado trên đám mây Dịch vụ web Amazon (AWS), bao gồm cả giấy phép.

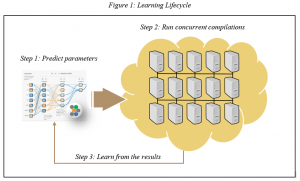

Công ty cũng sẽ trình diễn các cải tiến đối với phần mềm đóng thời gian InTime của mình để tối ưu hóa thời gian của FPGA trong đám mây (Hình 1). Phương pháp tối ưu hóa InTime có thể cải thiện tần số xung nhịp từ 20 đến 80% và đáp ứng các yêu cầu về thời gian trong vài ngày, thay vì hàng tuần thông qua học máy. Phần mềm cũng tăng tốc thời gian đóng và tối ưu hóa và được truy cập qua đám mây.

Công ty cũng sẽ trình diễn các cải tiến đối với phần mềm đóng thời gian InTime của mình để tối ưu hóa thời gian của FPGA trong đám mây (Hình 1). Phương pháp tối ưu hóa InTime có thể cải thiện tần số xung nhịp từ 20 đến 80% và đáp ứng các yêu cầu về thời gian trong vài ngày, thay vì hàng tuần thông qua học máy. Phần mềm cũng tăng tốc thời gian đóng và tối ưu hóa và được truy cập qua đám mây.

Thúc đẩy công nghệ eFPGA, Chất bán dẫn Ayncix đang hợp tác với chuyên gia IP CAST để tăng thông lượng và tiết kiệm bộ nhớ lưu trữ.

Hai nhà triển lãm sẽ giải thích cách IP nén không mất dữ liệu CAST đã được chuyển đến danh mục đầu tư Ayncix FPGA để sử dụng trong trung tâm dữ liệu và các ứng dụng truyền dữ liệu cạnh di động. Việc triển khai phần cứng của tiêu chuẩn nén không mất dữ liệu cho Deflate, GZIP và ZLIB, tương thích với các triển khai phần mềm được sử dụng để nén hoặc giải nén để cung cấp thông lượng lên tới 100Gbit / giây với độ nén thấp và độ trễ thấp, kết hợp với công nghệ SpeedFP eFPGA để di chuyển và lưu trữ lớn dữ liệu ở mức tiêu thụ điện năng thấp.

CAST đã chuyển IP của mình sang các GPU Ayncix

Hiệu suất năng lượng

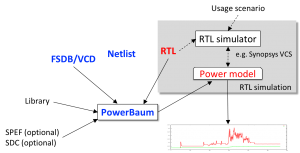

Nói về quản lý năng lượng, một nhà triển lãm khác, Baum, xác định hiệu quả năng lượng là lĩnh vực kém phát triển nhất trong thiết kế chip. Công cụ phân tích và mô hình năng lượng tự động của nó được thiết kế cho các dự án ô tô, IoT, di động, mạng và máy chủ. PowerBaum 2.0 (Hình 3) hỗ trợ năng lượng động và tĩnh, lấy các mô tả RTL và netlist và thêm hỗ trợ cho phân tích công suất với mô phỏng phần cứng. Điều này, cho biết công ty, cho phép các kỹ sư sửa lỗi điện trong các tình huống phần mềm thực tế. Công cụ này cũng hỗ trợ phân tích với nhiệt độ tùy ý được chỉ định bởi các nhà thiết kế, để đánh giá ảnh hưởng của nhiệt độ đến mức tiêu thụ năng lượng của thiết kế.

Tại DAC, công ty cũng sẽ giới thiệu PowerWurzel, một công cụ phân tích công suất cấp cổng được tích hợp với PowerBaum để mô hình hóa công suất.

Hình 3 Baum Công cụ phân tích hiệu quả năng lượng

Các công cụ xác minh và thiết kế SoC dựa trên đám mây cho thiết kế vi mạch từ Metrics bao gồm Trình mô phỏng và xác minh đám mây, được thiết kế để quản lý các yêu cầu và tài nguyên mô phỏng, điều chỉnh chúng lên hoặc xuống mỗi phút. Công ty tuyên bố rằng Google Cloud cho phép khả năng mô phỏng SystemVerilog không giới hạn UVM và quản lý xác minh dựa trên web để có thời gian hồi quy nhanh hơn, giảm lỗi mã trung kế và phạm vi bảo hiểm mã dự đoán.

Bên cạnh các nhà triển lãm, sự kiện này tổ chức các phiên kỹ thuật và một chương trình ghi chú giải quyết các lĩnh vực chủ đề. Ví dụ, năm nay, Cadence sẽ tổ chức một hướng dẫn về An toàn và độ tin cậy chức năng cho các ứng dụng ô tô, và một về học máy (Học máy mang lại hiệu suất nhận dạng giọng nói cho cấp độ tiếp theo). Một bài phát biểu của Anna-Katrina Shedletsky, Cụ, vào thứ Hai ngày 25 tháng 6, sẽ tập trung vào Tự động hóa trí thông minh: Học máy và Tương lai của Sản xuất. Sử dụng ML và AI cho robot hỗ trợ xã hội (SAR) được Maja Matarić, Đại học Nam California, người sẽ trình bày ‘Tự động hóa so với Augmented: Robotocs hỗ trợ xã hội và Tương lai của công việc.

Một bài phát biểu quan trọng khác ủng hộ RISC-V như một phương tiện để giải phóng các kiến trúc sư khỏi các kiến trúc tập lệnh độc quyền (ISAs). David A Patterson, Google và Đại học California, sẽ giới thiệu Age Thời đại hoàng kim mới cho kiến trúc máy tính: Máy gia tốc cụ thể miền và RISC-V rõ ràng.

Một lĩnh vực mới trong năm nay tại DAC là Thiết kế cơ sở hạ tầng. Sáng kiến của Liên minh ESD và Hiệp hội các chuyên gia tính toán hiệu năng cao là một lĩnh vực dành riêng cho cơ sở hạ tầng CNTT để thiết kế các hệ thống và linh kiện điện tử. Cũng như các yêu cầu về điện toán và lưu trữ để thiết kế và quản lý sử dụng đám mây, có một nhà hát gian hàng Thiết kế trên đám mây chuyên dụng thảo luận về quản lý giấy phép, điện toán lưới và bảo mật dữ liệu.