Zprávy

DAC zkoumá roli AI a ML na trzích

Moscone Center, San Francisco, bude hostit DAC 25. - 28. června

OneSpin Solutions a Austemper Design Systems zdůrazní nástroje pro ověření funkční bezpečnosti. Austemper se zaměří na vývoj kritických systémů s pomocí sady nástrojů KaleidoScope, která podporuje analogový design pro současné šíření poruch smíšeného signálu. Automatizovaná sada nástrojů má bezpečnostní analýzy, syntézu a ověřovací schopnosti pro aplikace orientované na certifikaci. Používá se pro velké automobilové designy v ADAS a autonomní jízdě. Simulace souběžných chyb zahrnuje simulace doporučené podle normy ISO 26262 pro splnění požadavků ASIL.

Společnost nedávno spolupracovala s OneSpin Solutions, aby přijala metodologii podporovanou nástroji pro funkční bezpečnostní aplikace kombinující tok návrhu a ověřování, který bude předveden na stánku OneSpin. Mechanické bezpečnostní mechanismy se vkládají do návrhů čipů a nástroje OneSpin Solutions formálně ověřují logiku hardwarové bezpečnosti. Kontrola ekvivalence zajišťuje, že vložená bezpečnostní logika neovlivňuje pravidelnou funkčnost a analýza detekce chyb ověřuje, že bezpečnostní mechanismy fungují správně v případě náhodných chyb.

OneSpin také propaguje svoji sadu nástrojů pro kvalifikaci nástrojů poté, co společnost TÜV SÜD ověřila své procesy vývoje nástrojů. Počáteční sada je k dispozici pro podnikový nástroj EDA 360 EC-FPGA, automatickou kontrolu ekvivalence, která zabraňuje toku návrhů FPGA v zavádění chyb implementace. Souprava je certifikována podle norem ISO 26262, IEC 61508 a EN 50128.

Statistiky FPGA

Stále s designem FPGA, Plunify spolupracoval s Xilinxem, aby nabídl návrhovou sadu Vivado v cloudu prostřednictvím platformy Plunify Cloud. Designéři zaplatí pouhých 50 c za sestavení projektu Vivado v cloudu Amazon Web Services (AWS), včetně licencí.

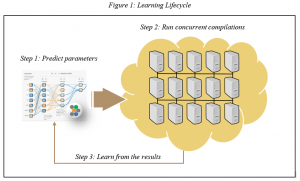

Společnost také předvede vylepšení svého softwaru pro uzavření časování InTime, aby optimalizovala načasování FPGA v cloudu (obrázek 1). Metodika optimalizace InTime může zlepšit frekvenci hodin o 20 až 80% a splnit požadavky na časování ve dnech, nikoli v týdnech pomocí strojového učení. Software také urychluje uzavření a optimalizaci časování a je přístupný prostřednictvím cloudu.

Společnost také předvede vylepšení svého softwaru pro uzavření časování InTime, aby optimalizovala načasování FPGA v cloudu (obrázek 1). Metodika optimalizace InTime může zlepšit frekvenci hodin o 20 až 80% a splnit požadavky na časování ve dnech, nikoli v týdnech pomocí strojového učení. Software také urychluje uzavření a optimalizaci časování a je přístupný prostřednictvím cloudu.

Achronix Semiconductor, který podporuje technologii eFPGA, spolupracuje s CAST specialistou na zvýšení propustnosti a úsporami v paměti.

Oba vystavovatelé vysvětlí, jak byla bezstratová IP komprese CAST přenesena do portfolia Achronix FPGA pro použití v aplikacích pro přenos dat v datových centrech a mobilních hranách. Hardwarová implementace bezeztrátového kompresního standardu pro Deflate, GZIP a ZLIB, je kompatibilní se softwarovými implementacemi používanými pro kompresi nebo dekompresi, která poskytuje propustnost až 100 Gbit / s s nízkou kompresí a nízkou latencí, spojená s technologií Speedcore eFPGA pro přesun a ukládání velkých data při nízké spotřebě energie.

CAST přenesl svou IP na FPGA Achronixu

Energetická účinnost

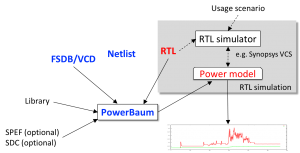

Když už mluvíme o řízení spotřeby, další vystavovatel, Baum, identifikuje energetickou účinnost jako nejrozvinutější oblast v designu čipů. Jeho automatizovaný nástroj pro analýzu a modelování výkonu je určen pro automobilové, IoT, mobilní, síťové a serverové projekty. PowerBaum 2.0 (obrázek 3) podporuje dynamický a statický výkon, přijímá popisy RTL a netlist a přidává podporu pro analýzu výkonu s emulací hardwaru. To, říká společnost, umožňuje technikům opravit chyby v napájení v realistických softwarových scénářích. Nástroj také podporuje analýzu s libovolnými teplotami, které jsou specifikovány konstruktéry, za účelem posouzení účinků teploty na spotřebu energie v návrhu.

V DAC uvede společnost také PowerWurzel, motor analýzy úrovně brány, který bude integrován s PowerBaum pro modelování výkonu.

Obrázek 3 Nástroje společnosti Baum analyzují energetickou účinnost

Cloudové nástroje pro návrh a ověřování SoC pro návrh IC od společnosti Metrics zahrnují Cloud Simulator a Verification Manager, který je navržen tak, aby spravoval požadavky na simulaci a zdroje a upravoval je každou minutu nahoru nebo dolů. Společnost prohlašuje, že Google Cloud umožňuje neomezenou simulační kapacitu SystemVerilog kompatibilní s UVM a nativní webovou verifikační správu pro rychlejší regresní doby, snížené chyby v kufru kódu a předvídatelné pokrytí kódem.

Kromě vystavovatelů se na akci konají také technické schůzky a program klíčových sdělení zaměřených na aktuální oblasti. V letošním roce bude například Cadence hostit výuku „Funkční bezpečnost a spolehlivost pro automobilové aplikace“ a výuku strojového učení („Strojové učení zvyšuje výkon rozpoznávání řeči na další úroveň“). V pondělí 25. června se hlavní projev Anny Katriny Šedletské, Instrumental, zaměří na „Automatizaci zpravodajských informací: Strojové učení a budoucnost výroby“. Použití ML a AI pro sociálně asistenční robotiku (SAR) je prozkoumáno ve čtvrteční hlavní přednášce Maja Matarićové z University of Southern California, která představí „Automatizace vs. augmentace: roboticky podporované sociální prostředky a budoucnost práce“.

Další klíčová myšlenka obhajuje RISC-V jako prostředek k osvobození architektů od proprietárních architektur instrukčních sad (ISA). David A Patterson, Google a Kalifornská univerzita, představí „Nový zlatý věk pro počítačovou architekturu: Domain specific Accelerators and Open RISC-V“.

Novinkou letošního roku v DAC je Alley Design Infrastructure Alley. Iniciativa ESD Alliance and Association for High-Performance Computing Professionals je oblast věnovaná IT infrastruktuře pro návrh elektronických systémů a komponent. Kromě požadavků na výpočetní a úložné prostory pro návrh a správu využití cloudu existuje i specializované pavilonové divadlo Design-on-the Cloud, které diskutuje o správě licencí, grid computingu a zabezpečení dat.