ニュース

DACは市場全体でAIとMLの役割を調査します

サンフランシスコのモスコーニセンターは、DACを6月25〜28日に開催します

OneSpin SolutionsとAustemper Design Systemsはどちらも、機能安全検証のためのツールを強調しています。 Austemperは、ミッションクリティカルなシステム開発に焦点を当てます。KaleidoScopeツールスイートは、同時の混合信号障害伝播のアナログ設計をサポートします。自動化されたツールスイートには、認証指向アプリケーション向けの安全性分析、合成、および検証機能があります。 ADASおよび自動運転の大規模な自動車設計に使用されます。同時故障シミュレーションには、ASIL要件に準拠するためにISO 26262で推奨されているシミュレーションが含まれます。

同社は最近OneSpin Solutionsと提携し、OneSpinブースでデモンストレーションされる設計と検証のフローを組み合わせて、機能安全アプリケーションのためのツールでサポートされた方法論を採用しました。ハードウェア安全メカニズムがチップ設計に挿入され、OneSpin Solutionsのツールがハードウェア安全ロジックを正式に検証します。同等性チェックは、挿入された安全ロジックが通常の機能に影響を与えないことを保証し、障害検出分析は、ランダムエラーが発生した場合に安全メカニズムが適切に機能することを確認します。

OneSpinは、TÜVSÜDによるツール開発プロセスの検証に続いて、ツール認定キットも宣伝しています。最初のキットは、同社の360 EC-FPGA EDAツールで利用できます。これは、FPGAデザインフローがインプリメンテーションエラーを発生させないようにする自動順次等価チェックです。このキットは、ISO 26262、IEC 61508、およびEN 50128の認定を受けています。

FPGAインサイト

引き続きFPGAデザインを使用して、Plunifyはザイリンクスと共同で、Plunify Cloudプラットフォームを介してクラウドでVivadoデザインスイートを提供しています。デザイナーは、ライセンスを含め、Amazon Web Services(AWS)クラウドでVivadoプロジェクトをコンパイルするためにわずか50cを支払います。

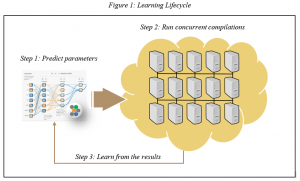

同社はまた、クラウド内のFPGAタイミングを最適化するために、InTimeタイミングクロージャソフトウェアの機能強化を実証します(図1)。 InTime最適化手法は、クロック周波数を20〜80%改善し、機械学習によって数週間ではなく数日でタイミング要件を満たします。ソフトウェアはまた、タイミングクロージャと最適化を加速し、クラウド経由でアクセスされます。

同社はまた、クラウド内のFPGAタイミングを最適化するために、InTimeタイミングクロージャソフトウェアの機能強化を実証します(図1)。 InTime最適化手法は、クロック周波数を20〜80%改善し、機械学習によって数週間ではなく数日でタイミング要件を満たします。ソフトウェアはまた、タイミングクロージャと最適化を加速し、クラウド経由でアクセスされます。

eFPGAテクノロジーを推進するAchronix Semiconductorは、IPスペシャリストCASTと協力して、スループットを向上させ、メモリストレージの節約を図っています。

2つの出展者は、CASTのロスレス圧縮IPがデータセンターおよびモバイルエッジデータ転送アプリケーションで使用するためにAchronix FPGAポートフォリオにどのように移植されているかを説明します。 Deflate、GZIP、およびZLIBのロスレス圧縮標準のハードウェア実装は、圧縮または解凍に使用されるソフトウェア実装と互換性があり、低圧縮および低レイテンシで最大100Gbit / sのスループットを提供し、Speedcore eFPGAテクノロジーと組み合わせて移動および格納します低消費電力でデータ。

CASTはそのIPをAchronixのFPGAに移植しました

エネルギー効率

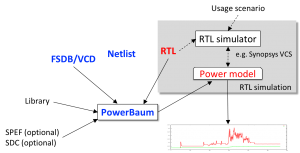

電力管理といえば、もう1つの出展者、バウムは、エネルギー効率をチップ設計で最も開発が進んでいない領域と見なしています。自動化された電力分析およびモデリングツールは、自動車、IoT、モバイル、ネットワーキング、およびサーバープロジェクト向けに設計されています。 PowerBaum 2.0(図3)は、RTLとネットリストの説明を取り入れて動的および静的電力をサポートし、ハードウェアエミュレーションによる電力分析のサポートを追加します。これにより、エンジニアは現実的なソフトウェアシナリオで電源のバグを修正できます。このツールは、設計者が指定した任意の温度での分析もサポートし、設計の消費電力に対する温度の影響を評価します。

DACでは、パワーモデリングのためにPowerBaumと統合されるゲートレベルの電力分析エンジンであるPowerWurzelも紹介します。

図3バウムのツールでエネルギー効率を分析

MetricsのIC設計用のクラウドベースのSoC設計および検証ツールには、シミュレーション要件とリソースを管理し、毎分上または下に調整するように設計されたCloud SimulatorおよびVerification Managerが含まれます。同社は、Google Cloudが無制限のUVM準拠のSystemVerilogシミュレーション機能と、回帰時間の短縮、トランクコードエラーの削減、予測可能なコードカバレッジのためのネイティブなWebベースの検証管理を可能にする、と主張しています。

出展者は別として、このイベントではテクニカルセッションと、話題の分野を取り上げた基調講演のプログラムが開催されます。たとえば、今年、ケイデンスは「自動車アプリケーションの機能的安全性と信頼性」に関するチュートリアルと機械学習に関するチュートリアルを主催します(「機械学習は音声認識パフォーマンスを次のレベルに引き上げます」)。 6月25日月曜日のInstrumentalであるAnna-Katrina Shedletskyによる基調講演では、「自動化インテリジェンス:機械学習と製造業の未来」に焦点を当てます。 MLとAIを使用して社会支援ロボット工学(SAR)を木曜日の基調講演で探る南カリフォルニア大学マハマタリッチは、「自動化vs拡張:社会支援ロボットと仕事の未来」を発表します。

別の基調講演では、独自の命令セットアーキテクチャ(ISA)からアーキテクトを解放する手段としてRISC-Vを提唱しています。 Googleとカリフォルニア大学のDavid A Pattersonが、「コンピュータアーキテクチャの新しい黄金時代:ドメイン固有のアクセラレータとOpen RISC-V」を発表します。

今年のDACの新しい領域は、デザインインフラストラクチャアレーです。 ESD Alliance and Association for High-Performance Computing Professionalsによるイニシアチブは、電子システムとコンポーネントの設計のためのITインフラストラクチャ専用の領域です。クラウドの使用を設計および管理するためのコンピューティングおよびストレージ要件に加えて、ライセンス管理、グリッドコンピューティング、およびデータセキュリティについて議論する専用のクラウド上のデザインパビリオンシアターがあります。