Vijesti

DAC istražuje ulogu AI i ML na tržištima

Moscone Center, San Francisco, bit će domaćin DAC-a od 25. do 28. lipnja

OneSpin Solutions i Austemper Design Systems oboje će istaknuti alate za provjeru funkcionalne sigurnosti. Austemper će se usredotočiti na razvoj kritičnog sustava, s KaleidoScope paketom alata koji podržava analogni dizajn za istodobno širenje kvarova mješovitim signalom. Automatizirani paket alata ima sigurnosne analize, sintezu i provjeru mogućnosti za certificirane aplikacije. Koristi se za velike automobilske dizajne u ADAS-u i autonomnoj vožnji. Istodobna simulacija grešaka uključuje simulacije koje je preporučio ISO 26262 u skladu sa ASIL zahtjevima.

Tvrtka je nedavno u partnerstvu s OneSpin Solutions-om usvojila metodologiju koja podržava alat za funkcionalne sigurnosne aplikacije, kombinirajući tijek dizajna i provjere, što će biti pokazano na štandu OneSpin-a. Hardverski sigurnosni mehanizmi umetnuti su u dizajne čipova, a alati OneSpin Solutions službeno provjeravaju logiku sigurnosti hardvera. Provjera ekvivalencije osigurava da umetnuta sigurnosna logika ne utječe na redovnu funkcionalnost, a analiza otkrivanja kvarova provjerava pravilno funkcioniranje sigurnosnih mehanizama u slučaju slučajnih pogrešaka.

OneSpin također promovira svoj komplet kvalifikacije alata, nakon što je TÜV SÜD potvrdio postupke razvoja alata. Početni komplet dostupan je za 360-godišnji alat tvrtke EDA-FPGA EDA, automatsku provjeru ekvivalentne provjere koja sprečava da FPGA dizajnerski tokovi uvode pogreške u implementaciji. Komplet je certificiran prema ISO 26262, IEC 61508 i EN 50128.

FPGA uvidi

Ipak s FPGA dizajnom, Plunify je surađivao s Xilinxom u ponudi dizajnerskog paketa Vivado u oblaku, preko Plunify Cloud platforme. Dizajneri plaćaju samo 50 c za sastavljanje Vivado projekta na oblaku Amazon Web Services (AWS), uključujući licence.

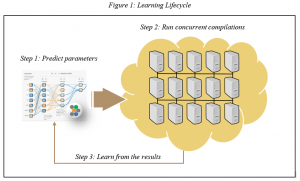

Tvrtka će također demonstrirati poboljšanja svog softvera za zatvaranje vremena InTime kako bi optimizirala FPGA vrijeme u oblaku (Slika 1). Metodologija optimizacije InTimea može poboljšati frekvenciju takta za 20 do 80% i udovoljiti zahtjevima vremena u danima, a ne tjednima putem strojnog učenja. Softver također ubrzava zatvaranje vremena i optimizaciju i pristupa se preko oblaka.

Tvrtka će također demonstrirati poboljšanja svog softvera za zatvaranje vremena InTime kako bi optimizirala FPGA vrijeme u oblaku (Slika 1). Metodologija optimizacije InTimea može poboljšati frekvenciju takta za 20 do 80% i udovoljiti zahtjevima vremena u danima, a ne tjednima putem strojnog učenja. Softver također ubrzava zatvaranje vremena i optimizaciju i pristupa se preko oblaka.

Promovišući eFPGA tehnologiju, Achronix Semiconductor surađuje s IP stručnjakom CAST kako bi povećao propusnost i uštedio u memoriji.

Dva izlagača objasnit će kako je CAST-ov IP kompresijski gubitak bez prenošenja u portfelj Achronix FPGA za upotrebu u podatkovnom centru i mobilnim aplikacijama za prijenos podataka. Hardverska primjena standarda kompresije bez gubitaka za Deflate, GZIP i ZLIB kompatibilna je s implementacijama softvera koji se koriste za kompresiju ili dekompresiju kako bi se osigurala do 100 Gbit / s propusnost s niskom kompresijom i malim kašnjenjem, zajedno s Speedcore eFPGA tehnologijom za pomicanje i spremanje velikih podaci pri maloj potrošnji energije.

CAST je svoj IP prenio na Achronix-ove FPGA-e

Energetska učinkovitost

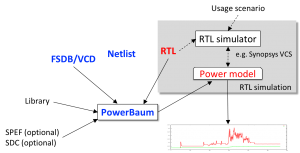

Govoreći o upravljanju energijom, drugi izlagač, Baum, identificira energetsku učinkovitost kao najnerazvijenije područje u dizajnu čipova. Automatski alat za analizu i modeliranje snage dizajniran je za automobilske, IoT, mobilne, mrežne i poslužiteljske projekte. PowerBaum 2.0 (slika 3) podržava dinamičku i statičku snagu uzimajući RTL i netlist opise te dodaje podršku za analizu snage hardverskom emulacijom. To, kažu iz tvrtke, omogućava inženjerima da popravljaju greške u napajanju u realnim softverskim scenarijima. Alat također podržava analizu s proizvoljnim temperaturama koje su odredili dizajneri, kako bi se procijenio utjecaj temperature na potrošnju energije dizajna.

U DAC-u će tvrtka predstaviti i PowerWurzel, motor za analizu snage na vratima koji će biti integriran u PowerBaum za modeliranje napajanja.

Slika 3. Baumovi alati analiziraju energetsku učinkovitost

Alat za dizajn i provjeru SoC za oblačenje IC dizajna iz tvrtke Metrics uključuje Cloud Simulator i Verification Manager, dizajniran za upravljanje zahtjevima i resursima simulacije, prilagođavajući ih gore ili dolje svake minute. Tvrtka tvrdi da Google Cloud omogućava neograničen kapacitet simulacije koji je u skladu sa UVM sustavom i izvorno, web-upravljanje provjerom za brže regresijsko vrijeme, smanjene pogreške kod prtljažnika i predvidljivu pokrivenost koda.

Uz izlagače, na manifestaciji se održavaju i tehničke sjednice i program glavnih tema koji se odnose na aktualna područja. Ove će godine, na primjer, Cadence ugostiti udžbenik o „Funkcionalnoj sigurnosti i pouzdanosti za automobilske aplikacije“, te jedan o strojnom učenju („Strojno učenje podiže performanse prepoznavanja govora na sljedeću razinu“). Glavni govor Anna-Katrina Shedletsky, Instrumental, u ponedjeljak, 25. lipnja, usredotočit će se na "Automatizacija inteligencije: Strojno učenje i budućnost proizvodnje". Upotreba ML i AI za socijalno potpunu robotiku (SAR) istražuje u četvrtak magistra Maja Matarić sa Sveučilišta u Južnoj Kaliforniji koja će predstaviti „Automatizacija vs povećanje: Socijalno pomoćni roboti i budućnost rada“.

Drugi glavni zagovornik zagovara RISC-V kao sredstvo za oslobađanje arhitekata od vlasničkih arhitektura skupa instrukcija (ISA). David A Patterson, Google i Kalifornijsko sveučilište, predstavit će „Novo zlatno doba za računalnu arhitekturu: Akceleratori specifični za domenu i Open RISC-V“.

Novo područje ove godine u DAC-u je Aleja dizajnerske infrastrukture. Inicijativa Saveza i ESD-a za udruženje profesionalaca za računalstvo visokih performansi područje je posvećeno IT infrastrukturi za dizajn elektroničkih sustava i komponenti. Kao i zahtjeve za računanjem i pohranom za dizajn i upravljanje upotrebom oblaka, postoji posvećeno kazalište paviljona Dizajn-u-oblaku, koje raspravlja o upravljanju licencama, računanju na mreži i sigurnosti podataka.