أخبار

تستكشف DAC دور الذكاء الاصطناعي و ML في الأسواق

سيستضيف مركز موسكون ، سان فرانسيسكو ، DAC 25-28 June

سوف يسلط كل من OneSpin Solutions وأنظمة تصميم Austemper كلاهما الضوء على أدوات للتحقق من السلامة الوظيفية. سيركز Austemper على تطوير النظام الحرج للمهمة ، مع مجموعة أدوات KaleidoScope التي تدعم التصميم التناظري لانتشار الأعطال المتزامنة والمتزامنة. تحتوي مجموعة الأدوات الآلية على قدرات تحليل السلامة والتوليف والتحقق للتطبيقات الموجهة للشهادة. يتم استخدامه لتصاميم السيارات على نطاق واسع في ADAS والقيادة المستقلة. تتضمن محاكاة الخطأ المتزامن المحاكاة الموصى بها من قبل ISO 26262 للتوافق مع متطلبات ASIL.

دخلت الشركة مؤخرًا في شراكة مع OneSpin Solutions لاعتماد منهجية مدعومة بالأداة لتطبيقات السلامة الوظيفية ، تجمع بين تدفق التصميم والتحقق ، والذي سيتم عرضه في كشك OneSpin. يتم إدراج آليات سلامة الأجهزة في تصميمات الرقائق ، وتتحقق أدوات OneSpin Solutions رسميًا من منطق سلامة الأجهزة. يضمن التحقق من التكافؤ أن منطق السلامة المدرج لا يؤثر على الوظائف المنتظمة ويثبت تحليل اكتشاف الأخطاء أن آليات السلامة تعمل بشكل صحيح في حالة حدوث أخطاء عشوائية.

تقوم OneSpin أيضًا بالترويج لمجموعة أدوات Tool Qualification الخاصة بها ، بعد التحقق من TÜV SÜD لعمليات تطوير الأداة. المجموعة الأولية متاحة لأداة 360 EC-FPGA EDA الخاصة بالشركة ، وهو فحص تكافؤ تسلسلي تلقائي يمنع تدفقات تصميم FPGA من تقديم أخطاء التنفيذ. المجموعة معتمدة من ISO 26262 و IEC 61508 و EN 50128.

رؤى FPGA

مع تصميم FPGA ، تعاونت Plunify مع Xilinx لتقديم مجموعة تصميم Vivado في السحابة ، عبر منصة Plunify Cloud. يدفع المصممون أقل من 50 سنتًا لتجميع مشروع Vivado على سحابة Amazon Web Services (AWS) ، بما في ذلك التراخيص.

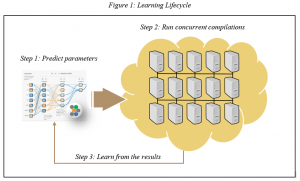

ستعرض الشركة أيضًا تحسينات على برنامج إغلاق توقيت InTime لتحسين توقيت FPGA في السحابة (الشكل 1). يمكن لمنهجية التحسين في InTime تحسين تردد الساعة بنسبة 20 إلى 80٪ وتلبية متطلبات التوقيت بالأيام ، بدلاً من أسابيع من خلال التعلم الآلي. يقوم البرنامج أيضًا بتسريع إغلاق التوقيت وتحسينه ويتم الوصول إليه عبر السحابة.

ستعرض الشركة أيضًا تحسينات على برنامج إغلاق توقيت InTime لتحسين توقيت FPGA في السحابة (الشكل 1). يمكن لمنهجية التحسين في InTime تحسين تردد الساعة بنسبة 20 إلى 80٪ وتلبية متطلبات التوقيت بالأيام ، بدلاً من أسابيع من خلال التعلم الآلي. يقوم البرنامج أيضًا بتسريع إغلاق التوقيت وتحسينه ويتم الوصول إليه عبر السحابة.

من خلال تعزيز تقنية eFPGA ، تتعاون Achronix Semiconductor مع متخصص IP IP CAST لزيادة الإنتاجية وتوفير في تخزين الذاكرة.

سيشرح العارضان كيف تم نقل IP للضغط بدون خسائر لـ CAST إلى محفظة Achronix FPGA للاستخدام في تطبيقات نقل البيانات من مركز البيانات والحافة المحمولة. يتوافق تطبيق الأجهزة لمعيار الضغط غير القابل للضياع لـ Deflate و GZIP و ZLIB مع عمليات تنفيذ البرامج المستخدمة للضغط أو إلغاء الضغط لتوفير إنتاجية تصل إلى 100 جيجابت / ثانية مع ضغط منخفض وزمن وصول منخفض ، إلى جانب تقنية Speedcore eFPGA للتحرك وتخزين كبير البيانات في استهلاك منخفض للطاقة.

قام CAST بنقل IP الخاص به إلى FPGAs الخاصة بـ Achronix

كفاءة الطاقة

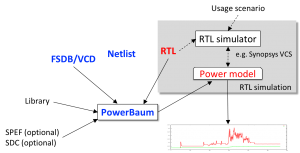

يتحدث عن إدارة الطاقة ، عارض آخر ، Baum ، تحديد كفاءة الطاقة باعتبارها المنطقة الأكثر تطورا في تصميم الرقائق. تم تصميم أداة تحليل الطاقة والنمذجة الآلية لمشاريع السيارات وإنترنت الأشياء والهواتف المحمولة والشبكات والخوادم. يدعم PowerBaum 2.0 (الشكل 3) الطاقة الديناميكية والثابتة ، مع أخذ أوصاف RTL و netlist ، ويضيف دعمًا لتحليل الطاقة باستخدام مضاهاة الأجهزة. هذا ، كما تقول الشركة ، يسمح للمهندسين بإصلاح أخطاء الطاقة في سيناريوهات البرامج الواقعية. تدعم الأداة أيضًا التحليل مع درجات الحرارة العشوائية التي يحددها المصممون ، لتقييم تأثيرات درجة الحرارة على استهلاك الطاقة في التصميم.

في DAC ، ستقدم الشركة أيضًا PowerWurzel ، وهو محرك تحليل طاقة على مستوى البوابة ليتم دمجه مع PowerBaum لنمذجة الطاقة.

الشكل 3 أدوات باوم تحلل كفاءة الطاقة

تتضمن أدوات SoC للتصميم والتحقق المستندة إلى السحابة لتصميم IC من Metrics ، Cloud Simulator و Verification Manager ، المصممة لإدارة متطلبات وموارد المحاكاة ، وتعديلها لأعلى أو لأسفل كل دقيقة. تدعي الشركة أن Google Cloud تتيح قدرة غير محدودة على محاكاة SystemVerilog المتوافقة مع UVM وإدارة التحقق الأصلية المستندة إلى الويب لأوقات الانحدار بشكل أسرع وتقليل أخطاء رمز الجذع وتغطية الشفرة التي يمكن التنبؤ بها.

وبصرف النظر عن العارضين ، يستضيف الحدث جلسات فنية وبرنامج من الكلمات الرئيسية التي تتناول المجالات المواضيعية. في هذا العام ، على سبيل المثال ، سيستضيف Cadence برنامجًا تعليميًا حول "السلامة الوظيفية والموثوقية لتطبيقات السيارات" ، وآخر حول التعلم الآلي ("التعلم الآلي يأخذ أداء التعرف على الكلام إلى المستوى التالي"). ستركز آنا-كاترينا شيدليتسكي ، أداة مفيدة ، يوم الاثنين 25 يونيو ، على "أتمتة الذكاء: التعلم الآلي ومستقبل التصنيع". تم استكشاف استخدام ML و AI للروبوتات المساعدة اجتماعيًا (SAR) في الكلمة الرئيسية التي ألقاها الخميس ماجا ماتاريتش ، جامعة جنوب كاليفورنيا ، والتي ستقدم "Automation vs Augmentation: Socially Assistive Robotocs and the Future of Work".

وتدعو كلمة رئيسية أخرى إلى RISC-V كوسيلة لتحرير المهندسين المعماريين من بنيات مجموعة تعليمات الملكية (ISAs). سيقدم David A Patterson من Google وجامعة كاليفورنيا "عصرًا ذهبيًا جديدًا لهندسة الكمبيوتر: المسرعات الخاصة بالمجال والمفتوحة RISC-V".

مجال جديد هذا العام في DAC هو زقاق البنية التحتية للتصميم. تعتبر مبادرة تحالف ESD ورابطة محترفي الحوسبة عالية الأداء مجالًا مخصصًا للبنية التحتية لتكنولوجيا المعلومات لتصميم الأنظمة والمكونات الإلكترونية. بالإضافة إلى متطلبات الحوسبة والتخزين لتصميم وإدارة استخدام السحابة ، هناك مسرح مخصص لجناح Design-on-the-Cloud يناقش إدارة الترخيص وحوسبة الشبكة وأمن البيانات.