Nyheder

DAC udforsker AI og ML's rolle på tværs af markederne

Moscone Center, San Francisco, er vært for DAC den 25.-28. Juni

OneSpin Solutions og Austemper Design Systems vil begge fremhæve værktøjer til funktionel sikkerhedsverifikation. Austemper vil fokusere på missionskritisk systemudvikling med KaleidoScope værktøjssæt, der understøtter analog design til samtidig, forplantning af blandet signalfejl. Den automatiserede værktøjssuite har sikkerhedsanalyse, syntese og verificeringsmuligheder til certificeringsorienterede applikationer. Det bruges til storskala bildesign i ADAS og autonom kørsel. Samtidig fejlsimulering inkluderer simuleringer, der er anbefalet af ISO 26262 for at overholde ASIL-kravene.

Virksomheden samarbejdede for nylig med OneSpin Solutions om at anvende en værktøjsstøttet metodologi til funktionelle sikkerhedsapplikationer, der kombinerer en design- og verificeringsflow, som vil blive demonstreret på OneSpin-standen. Hardware-sikkerhedsmekanismer indsættes i chipdesign, og OneSpin Solutions 'værktøjer formelt verificerer hardware-logikens hardware. Ækvivalenskontrol sikrer, at den indsatte sikkerhedslogik ikke påvirker regelmæssig funktionalitet, og fejldetekteringsanalyse verificerer, at sikkerhedsmekanismer fungerer korrekt i tilfælde af tilfældige fejl.

OneSpin promoterer også sit værktøjskvalificeringssæt efter verifikation fra TÜV SÜD af dets værktøjsudviklingsprocesser. Det indledende sæt er tilgængeligt for virksomhedens 360 EC-FPGA EDA-værktøj, en automatisk sekventiel ækvivalenskontrol, der forhindrer FPGA-designstrømme i at introducere implementeringsfejl. Sættet er certificeret i henhold til ISO 26262, IEC 61508 og EN 50128.

FPGA-indsigt

Stadig med FPGA-design har Plunify samarbejdet med Xilinx for at tilbyde Vivado-designpakken i skyen via Plunify Cloud-platformen. Designere betaler så lidt som 50c for at kompilere et Vivado-projekt i Amazon Web Services (AWS) sky, inklusive licenser.

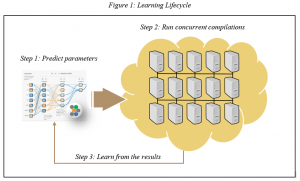

Virksomheden vil også demonstrere forbedringer af sin InTime-timing-lukningssoftware for at optimere FPGA-timing i skyen (figur 1). InTime Optimization Methodology kan forbedre urfrekvensen med 20 til 80% og imødekomme timingkrav i dage snarere end uger via maskinlæring. Softwaren accelererer også timing-lukning og optimering og fås adgang via skyen.

Virksomheden vil også demonstrere forbedringer af sin InTime-timing-lukningssoftware for at optimere FPGA-timing i skyen (figur 1). InTime Optimization Methodology kan forbedre urfrekvensen med 20 til 80% og imødekomme timingkrav i dage snarere end uger via maskinlæring. Softwaren accelererer også timing-lukning og optimering og fås adgang via skyen.

Achronix Semiconductor fremmer eFPGA-teknologi og samarbejder med IP-specialist CAST for at øge kapaciteten og spare besparelser i hukommelseslagring.

De to udstillere vil forklare, hvordan CAST's tabsfri komprimerings-IP er blevet portet til Achronix FPGA-porteføljen til brug i datacenter og mobile edge dataoverførselsapplikationer. Hardwareimplementeringen af den tabsfri komprimeringsstandard for Deflate, GZIP og ZLIB, er kompatibel med softwareimplementeringer, der bruges til komprimering eller dekomprimering for at give op til 100 Gbit / s gennemstrømning med lav komprimering og lav latens, kombineret med Speedcore eFPGA-teknologi til at flytte og opbevare store data ved et lavt strømforbrug.

CAST har portet sin IP til Achronix's FPGA'er

Energieffektivitet

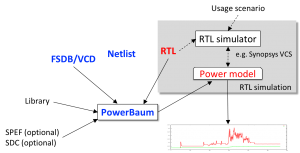

Når vi taler om strømstyring, identificerer en anden udstiller, Baum, energieffektivitet som det mest underudviklede område inden for chipdesign. Dets automatiserede effektanalyse- og modelleringsværktøj er designet til bil-, IoT-, mobil-, netværks- og serverprojekter. PowerBaum 2.0 (figur 3) understøtter dynamisk og statisk magt, indtager RTL- og netlistebeskrivelser og tilføjer support til strømanalyse med hardware-emulering. Dette, siger virksomheden, giver ingeniører mulighed for at løse strømfejl i realistiske softwarescenarier. Værktøjet understøtter også analyse med vilkårlige temperaturer, der er specificeret af designere, for at vurdere temperatureffekten på et designs strømforbrug.

Hos DAC vil virksomheden også introducere PowerWurzel, en motoranalysemotor til gate-niveau, der skal integreres med PowerBaum til strømmodellering.

Figur 3 Baums værktøjer analyserer energieffektivitet

Cloudbaseret SoC-design og verificeringsværktøjer til IC-design fra Metrics inkluderer Cloud Simulator and Verification Manager, designet til at styre simuleringskrav og ressourcer, justere dem op eller ned hvert minut. Virksomheden hævder, at Google Cloud muliggør ubegrænset UVM-kompatibel SystemVerilog-simuleringskapacitet og indbygget, webbaseret verificeringsstyring for hurtigere regressionstider, reducerede bagagerumskodefejl og forudsigelig kodedækning.

Bortset fra udstillere, arrangeres begivenheden tekniske sessioner og et program med grundlæggende henvisninger til aktuelle områder. I år er der for eksempel Cadence vært for en tutorial om 'Funktionel sikkerhed og pålidelighed til automobilapplikationer' og en om maskinlæring ('Maskinlæring tager ydeevne til talegenkendelse til næste niveau'). En hovednote af Anna-Katrina Shedletsky, Instrumental, mandag den 25. juni, vil fokusere på ‘Automating Intelligence: Machine Learning and the Future of Manufacturing’. Brug af ML og AI til socialt hjælpemæssig robotik (SAR) udforskes i torsdagens hovedtaler af Maja Matarić, University of South California, der vil præsentere 'Automation vs Augmentation: Socially Assistive Robotocs and the Future of Work'.

En anden hovednotat går ind for RISC-V som et middel til at frigøre arkitekter fra proprietære instruktionssætarkitekturer (ISA'er). David A Patterson, Google og University of California, præsenterer 'En ny guldalder til computerarkitektur: domænespecifikke acceleratorer og åben RISC-V'.

Et nyt område i år på DAC er Design Infrastructure Alley. Initiativet fra ESD Alliance og Association for High-Performance Computing Professionals er et område dedikeret til IT-infrastrukturen til design af elektroniske systemer og komponenter. Udover computerkrav og opbevaringskrav til design og styring af brugen af skyen, er der et dedikeret Design-on-the-Cloud-paviljongteater, der diskuterer licensstyring, net-computing og datasikkerhed.