haber

DAC, AI ve ML'nin pazarlardaki rolünü araştırıyor

Moscone Center, San Francisco, 25-28 Haziran DAC ev sahipliğinde

OneSpin Solutions ve Austemper Design Systems, işlevsel güvenlik doğrulaması için araçları vurgulayacaktır. Austemper, eşzamanlı, karışık sinyalli arıza yayılımı için analog tasarımı destekleyen KaleidoScope araç takımı ile kritik öneme sahip sistem geliştirmeye odaklanacak. Otomatik takım paketi, sertifika odaklı uygulamalar için güvenlik analizi, sentez ve doğrulama özelliklerine sahiptir. ADAS'ta büyük ölçekli otomotiv tasarımları ve otonom sürüş için kullanılır. Eşzamanlı hata simülasyonu, ASIL gerekliliklerine uymak için ISO 26262 tarafından önerilen simülasyonları içerir.

Şirket, OneSpin standında sergilenecek bir tasarım ve doğrulama akışını birleştirerek fonksiyonel güvenlik uygulamaları için araç destekli bir metodoloji benimsemek için son zamanlarda OneSpin Solutions ile ortaklık kurdu. Donanım güvenliği mekanizmaları yonga tasarımlarına yerleştirilir ve OneSpin Solutions’ın araçları donanım güvenliği mantığını resmi olarak doğrular. Eşdeğerlik kontrolü, eklenen güvenlik mantığının düzenli işlevselliği etkilememesini sağlar ve hata algılama analizi, rastgele hata durumunda güvenlik mekanizmalarının düzgün çalıştığını doğrular.

OneSpin, TÜV SÜD tarafından takım geliştirme süreçlerinin doğrulanmasının ardından Takım Yeterlilik kitini de tanıtmaktadır. İlk kit, şirketin 360 EC-FPGA EDA aracı için mevcut olup, FPGA tasarım akışlarının uygulama hataları vermesini engelleyen otomatik sıralı denklik kontrolü. Kit, ISO 26262, IEC 61508 ve EN 50128 sertifikalıdır.

FPGA bilgileri

Yine FPGA tasarımı ile Plunify, Plunify Cloud platformu aracılığıyla bulutta Vivado tasarım paketini sunmak için Xilinx ile işbirliği yaptı. Tasarımcılar Amazon Web Services (AWS) bulutunda lisanslar da dahil olmak üzere bir Vivado projesini derlemek için 50c kadar az ödeme yaparlar.

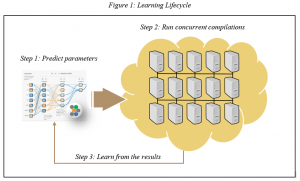

Şirket ayrıca bulutta FPGA zamanlamasını optimize etmek için InTime zamanlama kapatma yazılımında iyileştirmeler gösterecek (Şekil 1). InTime Optimizasyon Metodolojisi, makine öğrenimi yoluyla saat frekansını haftalar yerine% 20 ila 80 oranında artırabilir ve zamanlama gereksinimlerini günler içinde karşılayabilir. Yazılım ayrıca zamanlama kapanışını ve optimizasyonunu hızlandırır ve bulut üzerinden erişilir.

Şirket ayrıca bulutta FPGA zamanlamasını optimize etmek için InTime zamanlama kapatma yazılımında iyileştirmeler gösterecek (Şekil 1). InTime Optimizasyon Metodolojisi, makine öğrenimi yoluyla saat frekansını haftalar yerine% 20 ila 80 oranında artırabilir ve zamanlama gereksinimlerini günler içinde karşılayabilir. Yazılım ayrıca zamanlama kapanışını ve optimizasyonunu hızlandırır ve bulut üzerinden erişilir.

EFPGA teknolojisini destekleyen Achronix Semiconductor, iş hacmini artırmak ve bellek depolamada tasarruf sağlamak için IP uzmanı CAST ile işbirliği yapıyor.

İki katılımcı, veri merkezi ve mobil uç veri aktarımı uygulamalarında kullanmak üzere CAST’ın kayıpsız sıkıştırma IP'sinin Achronix FPGA portföyüne nasıl taşındığını açıklayacak. Deflate, GZIP ve ZLIB için kayıpsız sıkıştırma standardının donanım uygulaması, büyük sıkıştırma ve düşük gecikme ile 100Gbit / s'ye kadar verim sağlamak için sıkıştırma veya açma için kullanılan yazılım uygulamalarıyla uyumludur. düşük güç tüketiminde veri.

CAST IP'sini Achronix’in FPGA'larına taşıdı

Enerji verimliliği

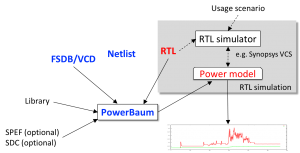

Başka bir katılımcı olan Baum, güç yönetiminden bahsetmişken, enerji verimliliğini yonga tasarımında en az gelişmiş alan olarak tanımlamaktadır. Otomatik güç analizi ve modelleme aracı otomotiv, IoT, mobil, ağ ve sunucu projeleri için tasarlanmıştır. PowerBaum 2.0 (Şekil 3), dinamik ve statik gücü destekler, RTL ve netlist açıklamalarını alır ve donanım öykünmesi ile güç analizi için destek ekler. Bu, şirketin mühendislerin gerçekçi yazılım senaryolarındaki güç hatalarını düzeltmelerine izin verdiğini söylüyor. Araç ayrıca, tasarımın güç tüketimi üzerindeki sıcaklığın etkilerini değerlendirmek için tasarımcılar tarafından belirlenen keyfi sıcaklıklarla analizi de destekler.

Şirket, DAC'da, güç modellemesi için PowerBaum ile entegre edilecek bir geçit seviyesi güç analiz motoru olan PowerWurzel'i de tanıtacak.

Şekil 3 Baum’un araçları enerji verimliliğini analiz eder

Metrics'ten IC tasarımı için bulut tabanlı SoC tasarım ve doğrulama araçları, simülasyon gereksinimlerini ve kaynaklarını yönetmek ve her dakika yukarı veya aşağı ayarlamak için tasarlanmış Bulut Simülatörü ve Doğrulama Yöneticisi'ni içerir. Şirket, Google Cloud'un daha hızlı regresyon süreleri, azaltılmış bagaj kodu hataları ve öngörülebilir kod kapsamı için sınırsız UVM uyumlu SystemVerilog simülasyon kapasitesi ve yerel, web tabanlı doğrulama yönetimi sağladığını iddia ediyor.

Etkinlik, katılımcıların yanı sıra, teknik oturumlara ve topikal alanlara yönelik bir anahtar not programına ev sahipliği yapıyor. Örneğin, bu yıl Cadence, 'Otomotiv Uygulamaları için İşlevsel Güvenlik ve Güvenilirlik' ve makine öğrenimi ('Makine Öğrenimi Konuşma Tanıma Performansını Bir Sonraki Seviyeye Taşıyor') üzerine bir eğitim sunacak. Enstrümantal Anna-Katrina Shedletsky'nin 25 Haziran Pazartesi günü yaptığı açılış konuşması, 'İstihbaratın Otomatikleştirilmesi: Makine Öğrenmesi ve Üretimin Geleceği' üzerine odaklanacak. Sosyal destekli robotlar (SAR) için ML ve AI kullanımı, Perşembe günkü Güney Kaliforniya Üniversitesi Maja Matarić tarafından ‘Otomasyon ve Arttırma: Sosyal Yardım Yardımcı Robotoclar ve İşin Geleceği’ ni sunacak.

Başka bir açılış konuşması RISC-V'yi mimarları tescilli öğretim seti mimarilerinden (ISA) kurtarmanın bir yolu olarak savunmaktadır. Google ve California Üniversitesi'nden David A Patterson, Computer Bilgisayar Mimarisinde Yeni Bir Altın Çağ: Alana Özel Hızlandırıcılar ve Açık RISC-V ’sunacak.

DAC'de bu yıl yeni bir alan Tasarım Altyapısı Yolu. ESD İttifakı ve Yüksek Performanslı Bilgi İşlem Uzmanları Derneği'nin girişimi, elektronik sistemlerin ve bileşenlerin tasarımı için BT altyapısına adanmış bir alandır. Bulutun tasarımı ve yönetimi için bilgi işlem ve depolama gereksinimlerinin yanı sıra, lisans yönetimi, şebeke bilgi işlem ve veri güvenliğini tartışan özel bir Bulut üzerinde Tasarım pavyon tiyatrosu vardır.