ข่าว

DAC สำรวจบทบาทของ AI และ ML ในตลาดต่างๆ

Moscone Center, ซานฟรานซิสโกจะเป็นเจ้าภาพ DAC 25-28 มิถุนายน

OneSpin Solutions และ Austemper Design Systems จะเน้นเครื่องมือสำหรับการตรวจสอบความปลอดภัยในการใช้งาน Austemper จะมุ่งเน้นไปที่การพัฒนาระบบที่มีความสำคัญต่อภารกิจด้วยชุดเครื่องมือ KaleidoScope ซึ่งรองรับการออกแบบอนาล็อกเพื่อการเผยแพร่สัญญาณความผิดพลาดแบบผสมพร้อมกัน ชุดเครื่องมืออัตโนมัติมีความสามารถในการวิเคราะห์ความปลอดภัยการสังเคราะห์และการตรวจสอบสำหรับการใช้งานที่มุ่งเน้นการรับรอง มันถูกใช้สำหรับการออกแบบยานยนต์ขนาดใหญ่ใน ADAS และการขับขี่แบบอิสระ การจำลองข้อผิดพลาดพร้อมกันรวมถึงการจำลองที่แนะนำโดย ISO 26262 เพื่อให้สอดคล้องกับข้อกำหนด ASIL

เมื่อเร็ว ๆ นี้ บริษัท ได้ร่วมมือกับ OneSpin Solutions เพื่อใช้วิธีการที่สนับสนุนเครื่องมือสำหรับการใช้งานด้านความปลอดภัยที่ใช้งานได้รวมการออกแบบและการตรวจสอบยืนยันซึ่งจะแสดงที่บูธ OneSpin มีการแทรกกลไกความปลอดภัยของฮาร์ดแวร์ลงในการออกแบบชิปและเครื่องมือของ OneSpin Solutions ตรวจสอบตรรกะความปลอดภัยของฮาร์ดแวร์อย่างเป็นทางการ การตรวจสอบความเท่าเทียมกันช่วยให้มั่นใจว่าตรรกะความปลอดภัยที่แทรกไว้ไม่มีผลต่อการทำงานปกติและการวิเคราะห์การตรวจจับข้อผิดพลาดตรวจสอบว่ากลไกความปลอดภัยทำงานได้อย่างถูกต้องในกรณีที่เกิดข้อผิดพลาดแบบสุ่ม

OneSpin ยังส่งเสริมชุดเครื่องมือการรับรองตามการตรวจสอบโดยTÜVSÜDของกระบวนการพัฒนาเครื่องมือ ชุดเริ่มต้นมีให้บริการสำหรับเครื่องมือ 360 EC-FPGA EDA ของ บริษัท การตรวจสอบลำดับความเท่ากันโดยอัตโนมัติที่ป้องกันไม่ให้กระแสการออกแบบ FPGA เกิดข้อผิดพลาดในการใช้งาน ชุดนี้ได้รับการรับรองมาตรฐาน ISO 26262, IEC 61508 และ EN 50128

ข้อมูลเชิงลึกของ FPGA

ยังคงมีการออกแบบ FPGA, Plunify ได้ร่วมมือกับ Xilinx เพื่อเสนอชุดการออกแบบ Vivado ในระบบคลาวด์ผ่านแพลตฟอร์ม Plunify Cloud นักออกแบบจ่ายเพียง 50c เพื่อคอมไพล์โครงการ Vivado บนคลาวด์ Amazon Web Services (AWS) รวมถึงใบอนุญาต

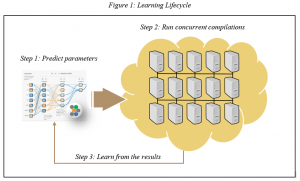

บริษัท จะสาธิตการปรับปรุงซอฟต์แวร์ปิดเวลาของ InTime เพื่อเพิ่มประสิทธิภาพการกำหนดเวลา FPGA ในคลาวด์ (รูปที่ 1) วิธีการเพิ่มประสิทธิภาพ InTime สามารถปรับปรุงความถี่สัญญาณนาฬิกาได้ 20 ถึง 80% และตอบสนองความต้องการด้านเวลาเป็นวันแทนที่จะเป็นสัปดาห์ผ่านการเรียนรู้ของเครื่อง ซอฟต์แวร์นี้ยังเร่งการปิดเวลาและการปรับให้เหมาะสมและเข้าถึงได้ผ่านทางคลาวด์

บริษัท จะสาธิตการปรับปรุงซอฟต์แวร์ปิดเวลาของ InTime เพื่อเพิ่มประสิทธิภาพการกำหนดเวลา FPGA ในคลาวด์ (รูปที่ 1) วิธีการเพิ่มประสิทธิภาพ InTime สามารถปรับปรุงความถี่สัญญาณนาฬิกาได้ 20 ถึง 80% และตอบสนองความต้องการด้านเวลาเป็นวันแทนที่จะเป็นสัปดาห์ผ่านการเรียนรู้ของเครื่อง ซอฟต์แวร์นี้ยังเร่งการปิดเวลาและการปรับให้เหมาะสมและเข้าถึงได้ผ่านทางคลาวด์

การส่งเสริมเทคโนโลยี eFPGA ทำให้ Achronix Semiconductor ร่วมมือกับ IP ผู้เชี่ยวชาญ CAST เพื่อเพิ่มปริมาณงานและประหยัดพื้นที่เก็บข้อมูลหน่วยความจำ

ผู้จัดแสดงสองคนจะอธิบายว่า IP การบีบอัด lossless แบบไม่สูญเสียของ CAST ได้รับการจัดส่งไปยังพอร์ต Achronix FPGA สำหรับใช้ในศูนย์ข้อมูลและแอปพลิเคชั่นถ่ายโอนข้อมูลบนมือถืออย่างไร การใช้งานฮาร์ดแวร์ของมาตรฐานการบีบอัดแบบไม่สูญเสียข้อมูลสำหรับ Deflate, GZIP และ ZLIB รองรับการใช้งานซอฟต์แวร์ที่ใช้สำหรับการบีบอัดหรือคลายการบีบอัดเพื่อให้ได้ถึง 100Gbit / s throughput ด้วยการบีบอัดต่ำและเวลาแฝงที่ต่ำ ข้อมูลที่ใช้พลังงานต่ำ

นักแสดงได้ส่ง IP ไปยัง FPGA ของ Achronix แล้ว

ประสิทธิภาพการใช้พลังงาน

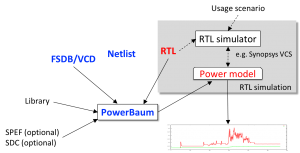

Baum ผู้จัดแสดงสินค้ารายอื่นกล่าวถึงการจัดการพลังงานซึ่งระบุถึงประสิทธิภาพการใช้พลังงานเป็นพื้นที่ที่มีการพัฒนาน้อยที่สุดในการออกแบบชิป เครื่องมือวิเคราะห์และสร้างแบบจำลองพลังงานอัตโนมัติถูกออกแบบมาสำหรับยานยนต์ IoT มือถือระบบเครือข่ายและเซิร์ฟเวอร์ PowerBaum 2.0 (รูปที่ 3) รองรับพลังงานแบบไดนามิกและแบบคงที่โดยใช้คำอธิบาย RTL และ netlist และเพิ่มการรองรับการวิเคราะห์พลังงานด้วยการจำลองฮาร์ดแวร์ สิ่งนี้กล่าวว่า บริษัท อนุญาตให้วิศวกรแก้ไขข้อบกพร่องด้านพลังงานในสถานการณ์จำลองซอฟต์แวร์ที่สมจริง เครื่องมือนี้ยังสนับสนุนการวิเคราะห์ที่มีอุณหภูมิตามอำเภอใจซึ่งนักออกแบบระบุไว้เพื่อประเมินผลกระทบของอุณหภูมิที่มีต่อการใช้พลังงานของการออกแบบ

ที่ DAC บริษัท จะแนะนำ PowerWurzel ซึ่งเป็นเครื่องมือวิเคราะห์พลังงานระดับประตูที่จะรวมเข้ากับ PowerBaum สำหรับการสร้างแบบจำลองพลังงาน

เครื่องมือของ Baum รูปที่ 3 วิเคราะห์ประสิทธิภาพการใช้พลังงาน

เครื่องมือการออกแบบและตรวจสอบ SoC บนคลาวด์สำหรับการออกแบบ IC จาก Metrics รวมถึง Cloud Simulator และ Verification Manager ที่ออกแบบมาเพื่อจัดการความต้องการการจำลองและทรัพยากรการปรับขึ้นหรือลงทุกนาที บริษัท อ้างว่า Google Cloud รองรับความสามารถในการจำลองแบบ SystemVerilog ตามมาตรฐาน UVM และการจัดการการตรวจสอบความถูกต้องบนเว็บแบบเนชั่นสำหรับเวลาการถดถอยที่เร็วขึ้นลดข้อผิดพลาดของรหัสลำตัวและรหัสครอบคลุมที่คาดการณ์ได้

นอกเหนือจากผู้จัดแสดงแล้วงานนี้ยังมีการจัดประชุมทางเทคนิคและโปรแกรมของการกล่าวสุนทรพจน์ในหัวข้อเฉพาะต่างๆ ตัวอย่างเช่นในปีนี้ Cadence จะเป็นเจ้าภาพการสอนเกี่ยวกับ 'ความปลอดภัยและความน่าเชื่อถือในการใช้งานสำหรับยานยนต์' และอีกหนึ่งการเรียนรู้ของเครื่อง ('การเรียนรู้ของเครื่องใช้ประสิทธิภาพการรู้จำเสียงพูดในระดับถัดไป') ปาฐกถาพิเศษโดย Anna-Katrina Shedletsky, Instrumental ในวันจันทร์ที่ 25 มิถุนายนจะมุ่งเน้นไปที่ 'ระบบอัตโนมัติอัจฉริยะ: การเรียนรู้ของเครื่องและอนาคตของการผลิต' การใช้ ML และ AI สำหรับหุ่นยนต์ช่วยเหลือทางสังคม (SAR) ได้รับการสำรวจในประเด็นสำคัญของวันพฤหัสบดีโดย Maja Matarićมหาวิทยาลัยเซาเทิร์นแคลิฟอร์เนียซึ่งจะนำเสนอ ‘Automation vs Augmentation: Robotist ช่วยชีวิตและอนาคตของการทำงาน

คำปราศรัยอื่นสนับสนุน RISC-V เพื่อให้สถาปนิกเป็นอิสระจากสถาปัตยกรรมชุดคำสั่งที่เป็นกรรมสิทธิ์ (ISAs) David A Patterson, Google และ University of California จะนำเสนอ "ยุคทองใหม่สำหรับสถาปัตยกรรมคอมพิวเตอร์: ตัวเร่งความเร็วเฉพาะโดเมนและ Open RISC-V"

พื้นที่ใหม่ในปีนี้ที่ DAC คือตรอกออกแบบโครงสร้างพื้นฐาน ความคิดริเริ่มโดย ESD Alliance and Association สำหรับผู้เชี่ยวชาญด้านคอมพิวเตอร์ประสิทธิภาพสูงเป็นพื้นที่ที่อุทิศให้กับโครงสร้างพื้นฐานด้านไอทีสำหรับการออกแบบระบบอิเล็กทรอนิกส์และส่วนประกอบ เช่นเดียวกับข้อกำหนดด้านการใช้คอมพิวเตอร์และการจัดเก็บข้อมูลสำหรับการออกแบบและการจัดการการใช้งานคลาวด์มีโรงละครศาลา Design-on-the-Cloud โดยเฉพาะที่กล่าวถึงการจัดการใบอนุญาตการคำนวณกริดและความปลอดภัยของข้อมูล