# **IGLOO2** Pin Descriptions

## **User I/Os**

IGLOO<sup>®</sup>2 field programmable gate array (FPGA) devices feature a flexible I/O structure that supports a range of mixed voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V) through bank selection. The MSIO, MSIOD, and DDRIO can be configured as differential I/Os or two single-ended I/Os. These I/Os use one I/O slot to implement single-ended standards and two I/O slots for differential standards.

For functional block diagrams of MSIO, MSIOD, and DDRIO, refer to the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

For supported I/O standards, refer to the "Supported Voltage Standards" table in the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

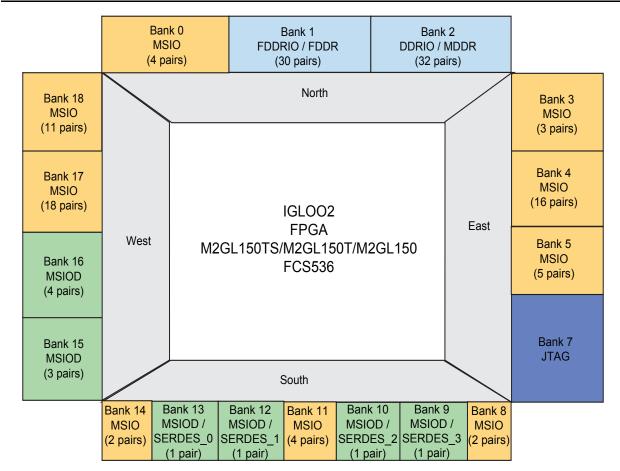

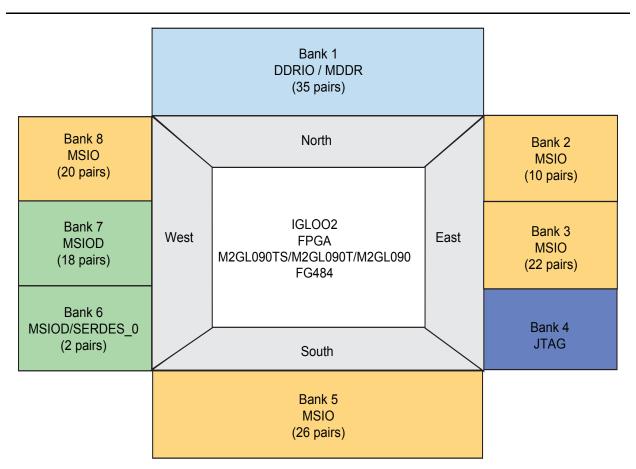

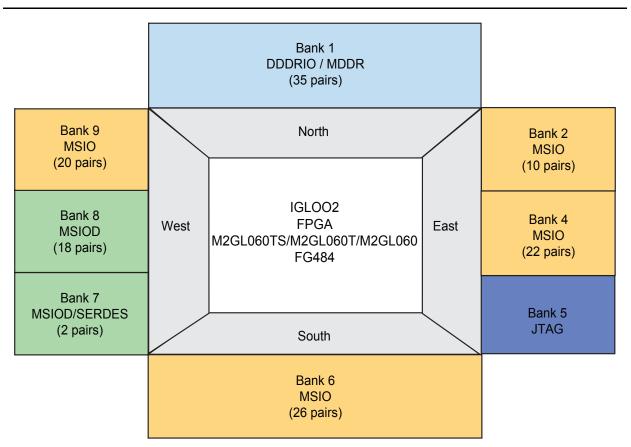

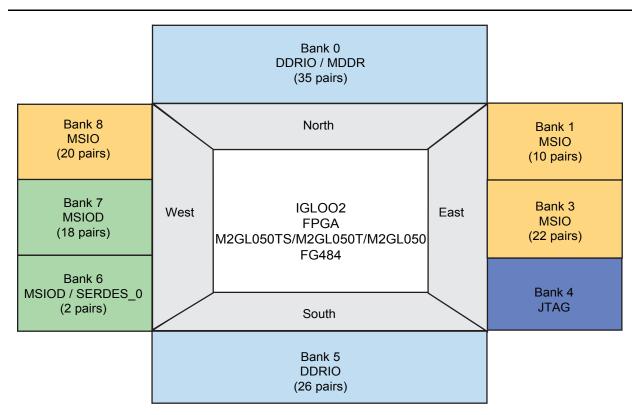

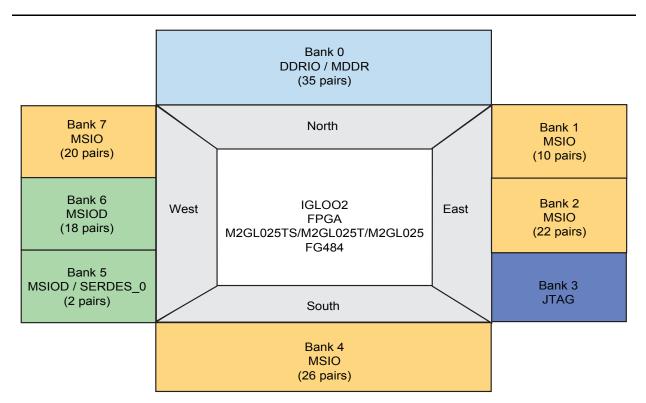

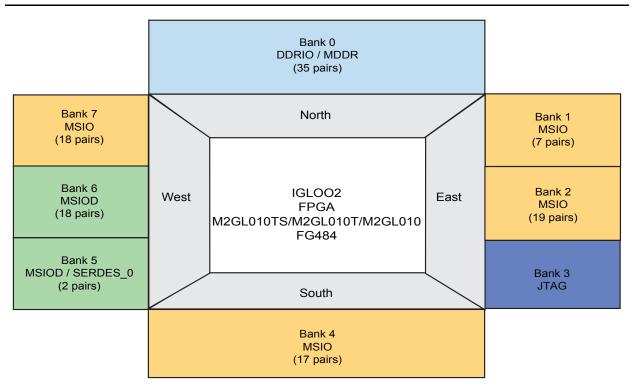

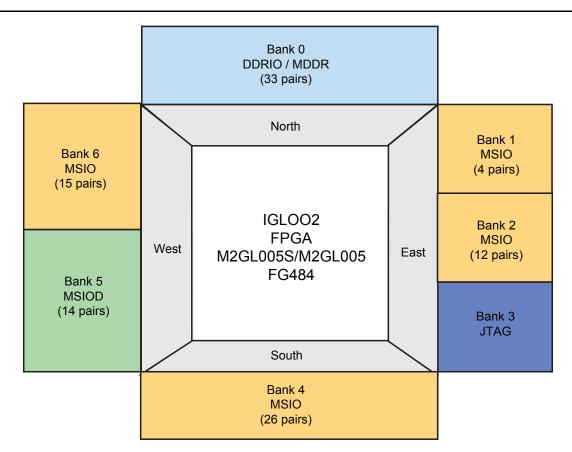

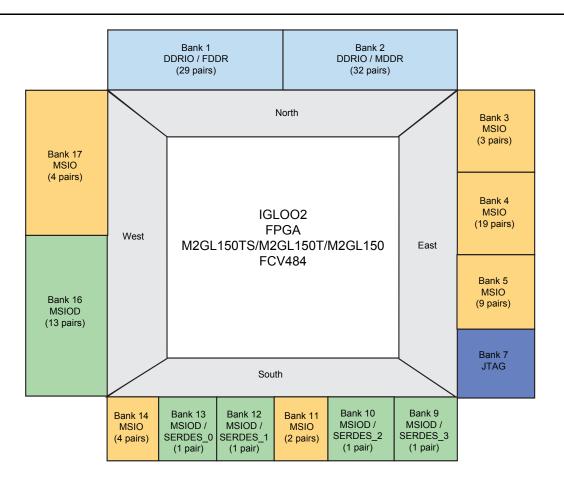

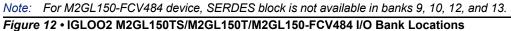

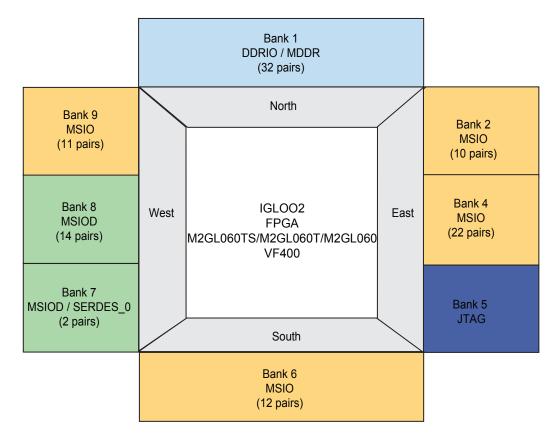

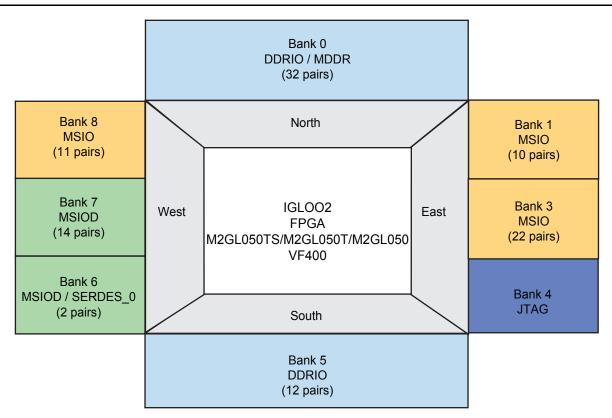

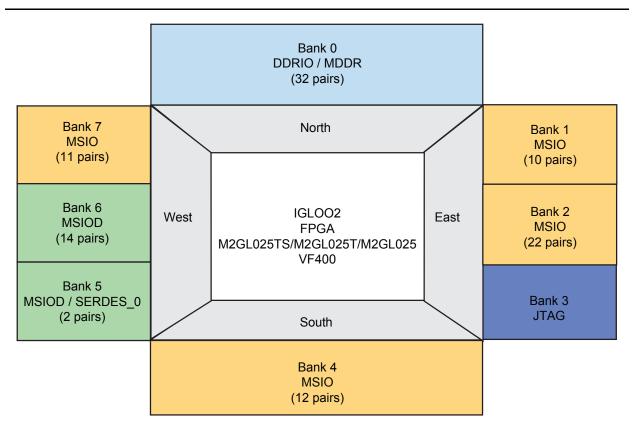

## **Bank Location Diagrams**

I/Os are grouped on the basis of I/O voltage standard. The grouped I/Os of each voltage standard form an I/O bank. Each I/O bank has dedicated I/O supply and ground voltages. Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank.

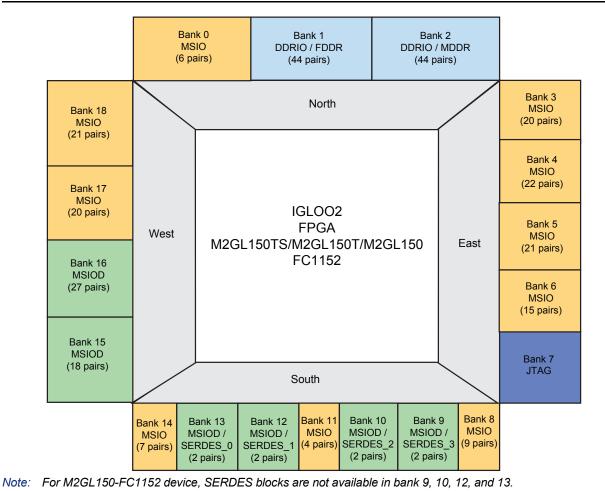

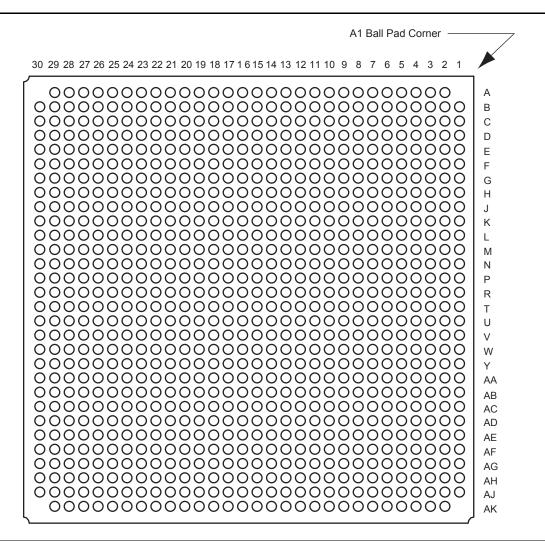

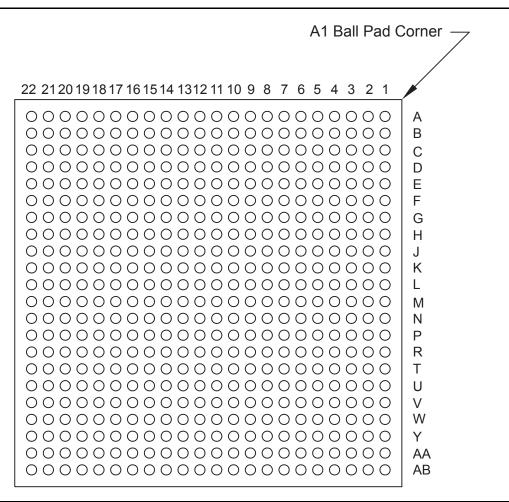

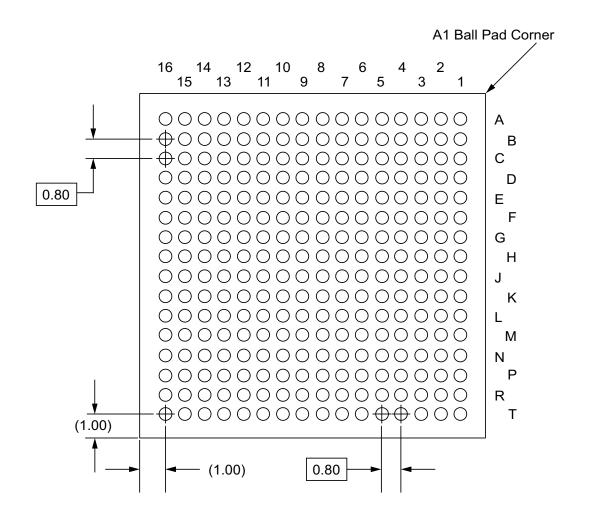

Figure 1 • IGLOO2 M2GL150TS/M2GL150T/M2GL150-FC1152 I/O Bank Locations

- 1. In bank 1, there are 21 single-ended user I/Os. Pin H27, MSI46NB1, cannot be configured as differential. The function MSI46NB1 is an input only pin.

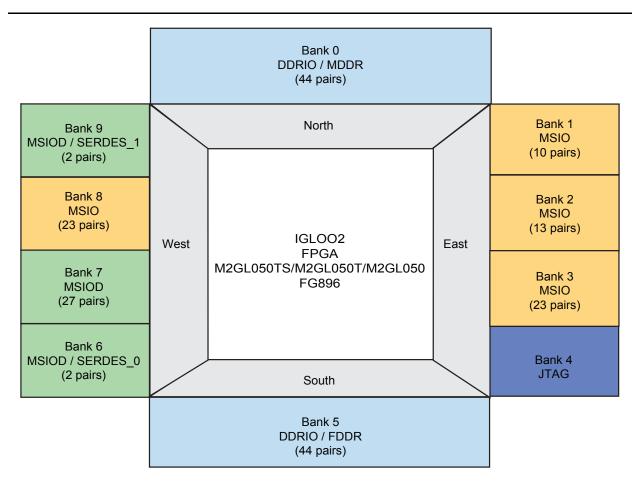

- 2. For M2GL050-FG896 device, SERDES blocks are not available in bank 6 and bank 9.

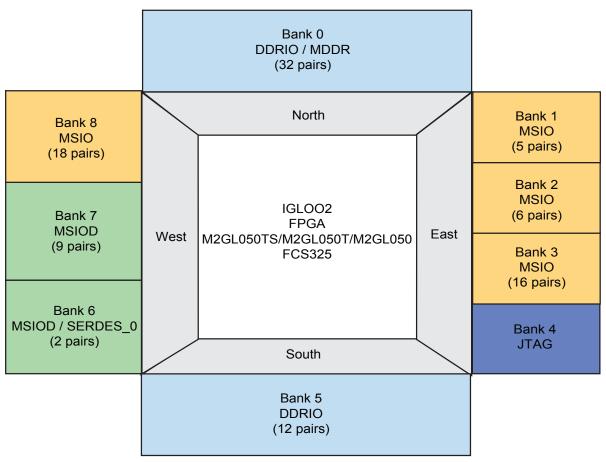

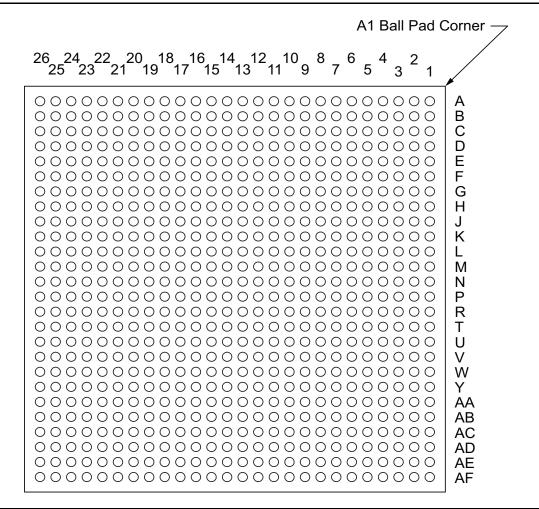

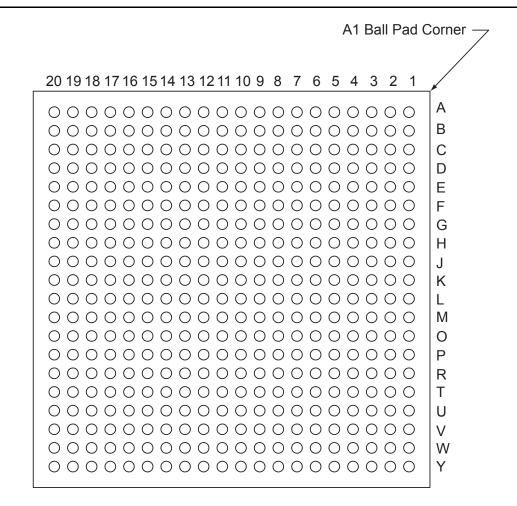

Figure 2 • IGLOO2 M2GL050TS/M2GL050T/M2GL050-FG896 I/O Bank Locations

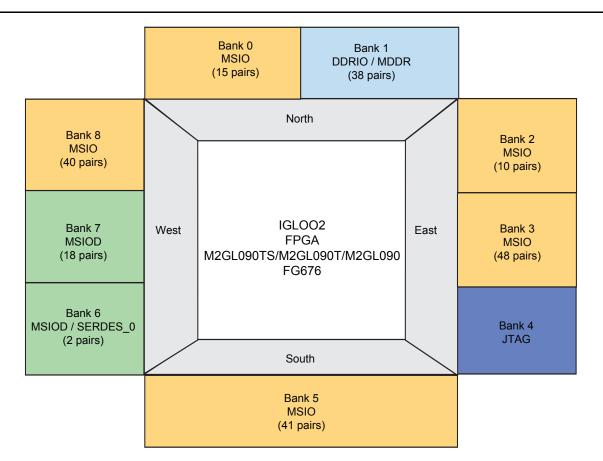

- 1. In bank 2, there are 21 single-ended user I/Os. Pin D23 and MSI59NB2 cannot be configured as differential. The function MSI59NB2 is an input only pin.

- 2. For M2GL090-FG676 device, the SERDES block is not available in bank 6.

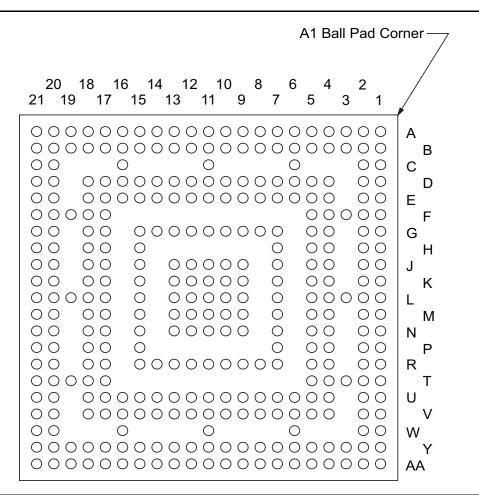

Figure 3 • IGLOO2 M2GL090TS/M2GL090T/M2GL090-FG676 I/O Bank Locations

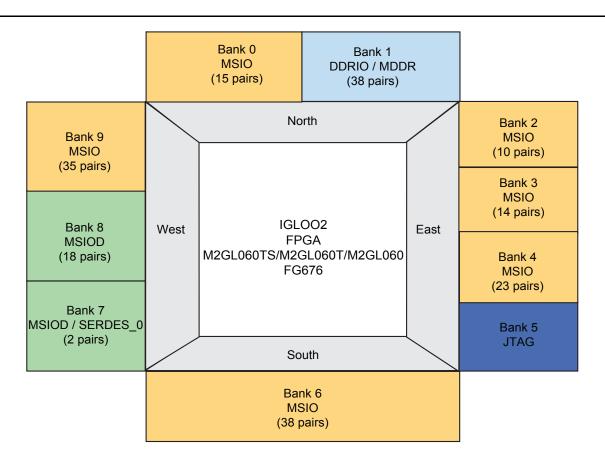

1. For M2GL060-FG676 device, SERDES block is not available in bank 7.

Figure 4 • IGLOO2 M2GL060TS/ M2GL060T/M2GL060-FG676 I/O Bank Locations

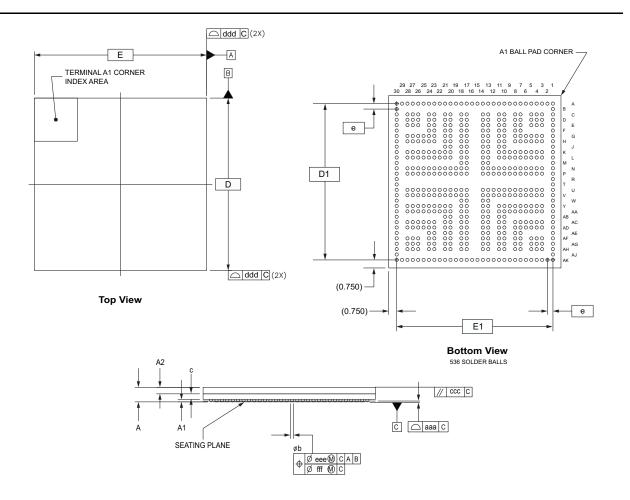

1. For M2GL150-FCS536 device, SERDES interface is not available in bank 9, 10,12, and 13.

Figure 5 • IGLOO2 M2GL150TS/M2GL150T/M2GL150-FCS536 I/O Bank Locations

- 1. In bank 2, there are 21 single-ended user I/Os. Pin D21, MSI59NB2, cannot be configured as differential. The function MSI59NB2 is an input only pin.

- 2. For M2GL090-FG484 device, SERDES block is not available in bank 6.

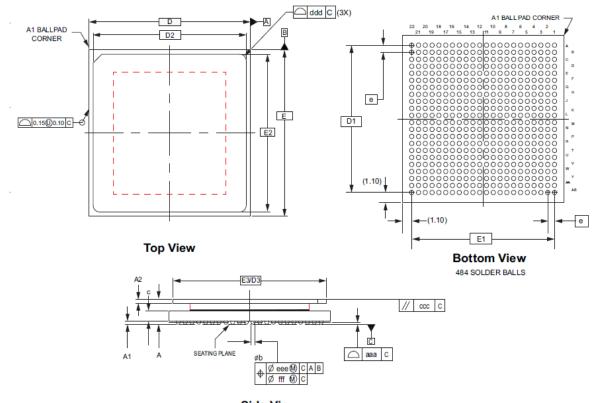

Figure 6 • IGLOO2 M2GL090TS/M2GL090T/M2GL090-FG484 I/O Bank Locations

- 1. In bank 2, there are 21 single-ended user I/Os. Pin D21, MSI47NB2, cannot be configured as differential. The function MSI47NB2 is an input only pin.

- 2. For the M2GL060S-FG484 and M2GL060-FG484 devices, SERDES block is not available in bank 7.

Figure 7 • IGLOO2 M2GL060TS/M2GL060T/M2GL060-FG484 I/O Bank Locations

1. In bank 1, there are 21 single-ended user I/Os. Pin D21, MSI46NB1, cannot be configured as differential. The function MSI46NB1 is an input only pin.

2. For M2GL050-FG484 device, SERDES block is not available in bank 6.

Figure 8 • IGLOO2 M2GL050TS/M2GL050T/M2GL050-FG484 I/O Bank Locations

- 1. In bank 1, there are 21 single-ended user I/Os. Pin D21, MSI32NB1, cannot be configured as differential. The function MSI32NB1 is an input only pin.

- 2. For M2GL025-FG484 device, SERDES block is not available in bank 5.

Figure 9 • IGLOO2 M2GL025TS/M2GL025T/M2GL025-FG484 I/O Bank Locations

1. In bank 1, there are 15 single-ended user I/Os. Pin D21, MSI26NB1, cannot be configured as differential. The function MSI32NB1 is an input only pin.

2. For M2GL010-FG484 device, SERDES block is not available in bank 5.

Figure 10 • IGLOO2 M2GL010TS/M2GL010T/M2GL010-FG484 I/O Bank Locations

- 1. In bank 1, there are 9 single-ended user I/Os. Pin D21 and MSI16NB1 cannot be configured as differential.

- 2. The function MSI16NB1 is an input only pin.

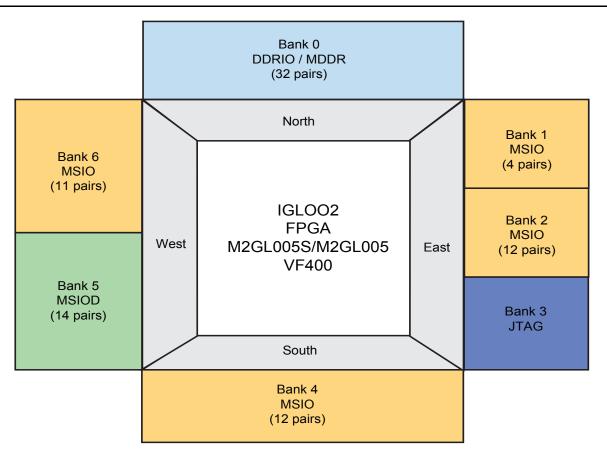

Figure 11 • IGLOO2 M2GL005S/M2GL005-FG484 I/O Bank Locations

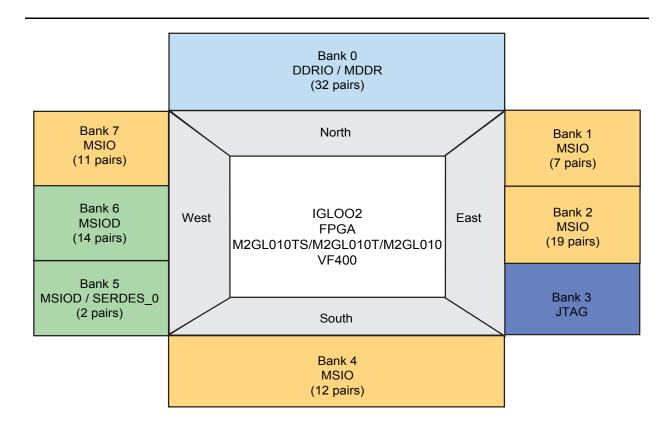

Note: For M2GL060-VF400 device, SERDES block is not available in bank 7.

Figure 13 • IGLOO2 M2GL060TS/M2GL060T/M2GL060-VF400 I/O Bank Locations

- 1. In bank 1, there are 21 single-ended user I/Os. Pin D18, MSI46NB1, cannot be configured as differential. The function MSI46NB1 is an input only pin.

- 2. For M2GL050-VF400 device, SERDES block is not available in bank 6.

Figure 14 • IGLOO2 M2GL050TS/M2GL050T/M2GL050-VF400 I/O Bank Locations

- 1. In bank 1, there are 21 single-ended user I/Os. Pin D18, MSI32NB1, cannot be configured as differential. The function MSI32NB1 is an input only pin.

- 2. For M2GL025-VF400 device, SERDES block is not available in bank 5.

Figure 15 • IGLOO2 M2GL025TS/M2GL025T/M2GL025-VF400 I/O Bank Locations

- 1. In bank 1, there are 15 single-ended user I/Os. Pin- D18, MSI26NB1, cannot be configured as differential. The function MSI26NB1 is an input only pin.

- 2. For M2GL010-VF400 device, SERDES block is not available in bank 5.

Figure 16 • IGLOO2 M2GL010TS/M2GL010T/M2GL010-VF400 I/O Bank Locations

- 1. In bank 1, there are 9 single-ended user I/Os. Pin D18, MSI16NB1 cannot be configured as differential.

- 2. The function MSI16NB1 is an input only pin.

Figure 17 • IGLOO2 M2GL005S/M2GL005-VF400 I/O Bank Locations

```

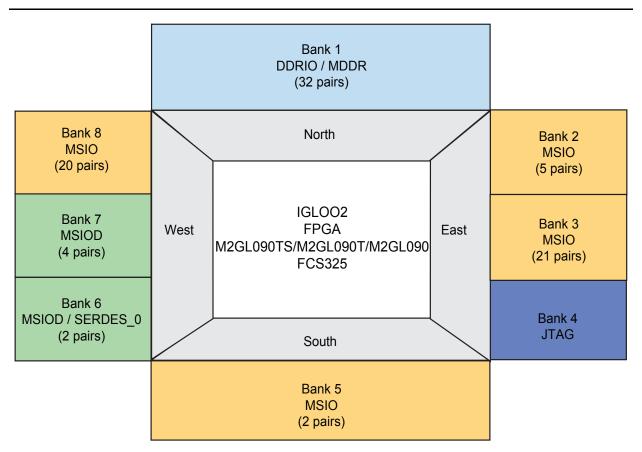

Note: For M2GL090-FCS325 device, SERDES block is not available in bank 6.

```

Figure 18 • IGLOO2 M2GL090TS/M2GL090T/M2GL090-FCS325 I/O Bank Locations

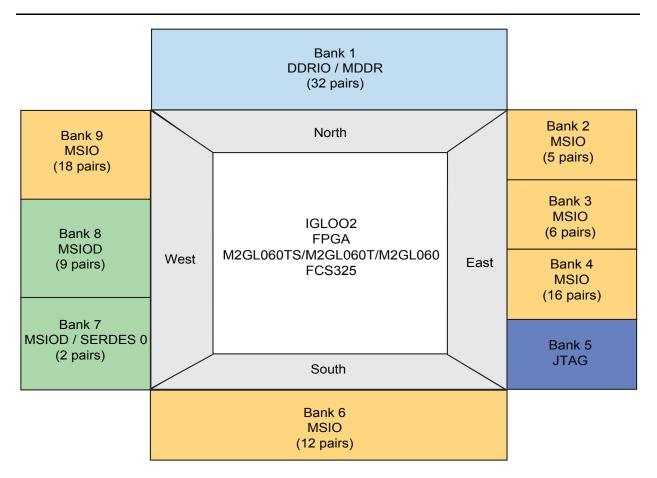

```

Note: For M2GL060-FCS325 device, SERDES block is not available in bank 7.

```

Figure 19 • IGLOO2 M2GL060TS/M2GL060T/M2GL060-FCS325 I/O Bank Locations

Note: For M2GL050-FCS325 device, SERDES block is not available in bank 6.

Figure 20 • IGLOO2 M2GL050TS/M2GL050T/M2GL050-FCS325 I/O Bank Locations

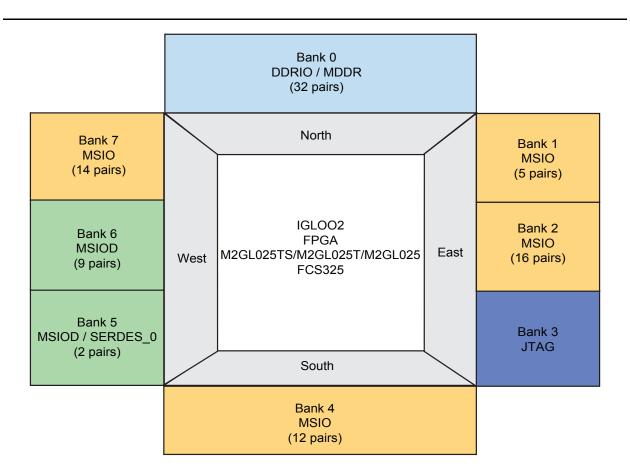

*Note:* For M2GL025-FCS325 device, SERDES block is not available in bank 5.

Figure 21 • IGLOO2 M2GL025TS/M2GL025T/M2GL025-FCS325 I/O Bank Locations

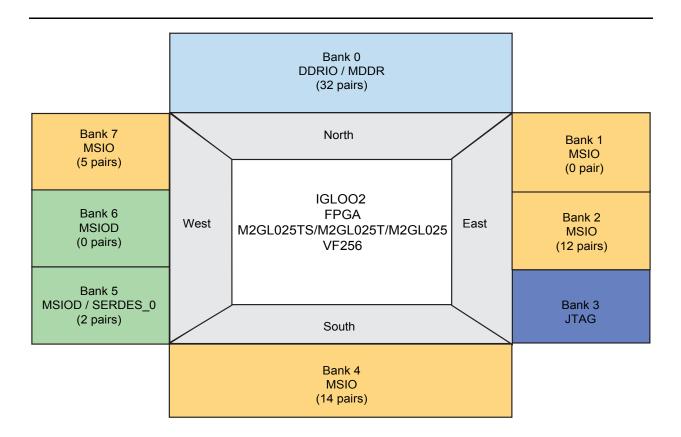

- 1. In bank 1, there are 4 single-ended user I/Os. Pin G12, MSIO32NB1 cannot be configured as differential. The function MSI32NB1 is an input only pin.

- 2. For M2GL025-VF256 device, SERDES block is not available in bank 5.

Figure 22 • IGLOO2 M2GL025TS/M2GL025T/M2GL025-VF256 I/O Bank Locations

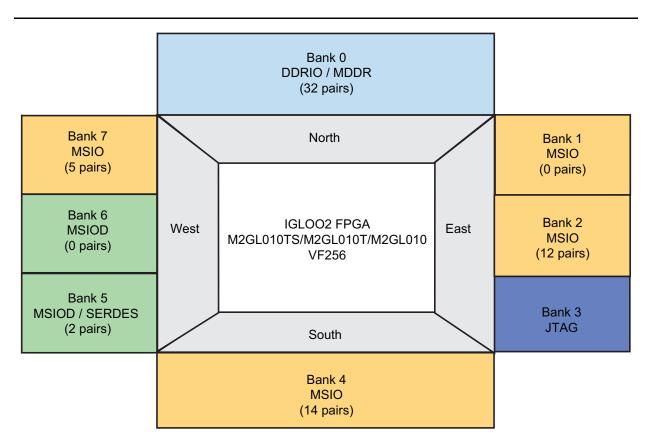

1. In bank 1, there are 4 single-ended user I/Os. Pin G12, MSI26NB1 cannot be configured as differential. The function MSI26NB1 is an input only pin.

2. For M2GL010-VF256 device, SERDES block is not available in bank 5.

Figure 23 • IGLOO2 M2GL010TS/M2GL010T/M2GL010-VF256 I/O Bank Locations

Note: In bank 1, there are 9 single-ended user I/Os. Pin D12, MSI16NB1 cannot be configured as differential. The function MSI16NB1 is an input only pin.

Figure 24 • IGLOO2 M2GL005S/M2GL005-VF256 I/O Bank Locations

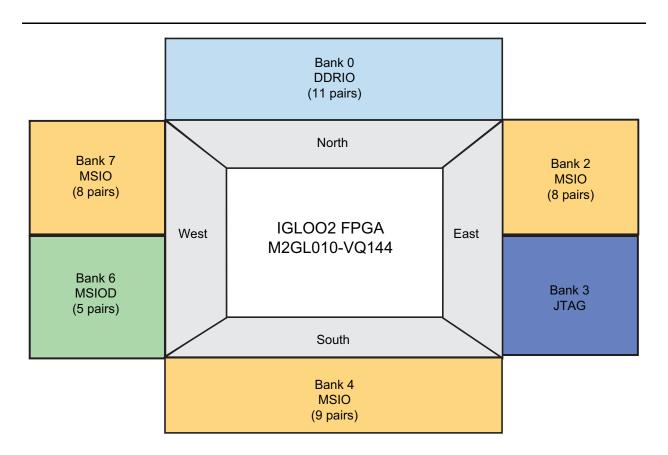

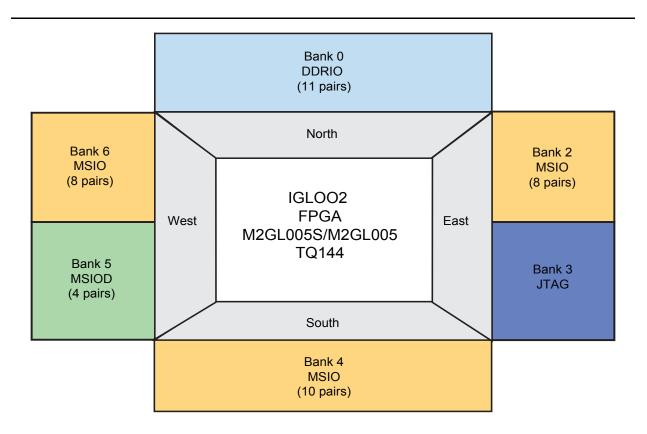

Figure 25 • IGLOO2 M2GL010-TQ144 I/O Bank Locations

Figure 26 • IGLOO2 M2GL005S/M2GL005-TQ144 I/O Bank Locations

|          | FC1152                           | FC1152 FG896 FG676               |                                  | FCS536                           | FCV484                           |                                  |                                  | FG48                             | 34                               |                                  |                                  |                             |

|----------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-----------------------------|

| Bank No. | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL050TS<br>M2GL050T<br>M2GL050 | M2GL090TS<br>M2GL090T<br>M2GL090 | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL090TS<br>M2GL090T<br>M2GL090 | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL050TS<br>M2GL050T<br>M2GL050 | M2GL025TS<br>M2GL050T<br>M2GL025 | M2GL010TS<br>M2GL010T<br>M2GL010 | M2GL005S                    |

| Bank 0   | MSIO:<br>fabric                  | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | _                                | -                                | _                                | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric |

| Bank 1   | DDRIO:<br>FDDR or<br>fabric      | MSIO:<br>fabric                  | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>FDDR or<br>fabric      | DDRIO:<br>FDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             |

| Bank 2   | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             |

| Bank 3   | MSIO:<br>fabric                  |                                  | MSIO:<br>fabric                  | JTAG/<br>SWD                     | JTAG/<br>SWD                     | JTAG/<br>SWD                |

| Bank 4   | MSIO:<br>fabric                  | JTAG/<br>SWD                     | JTAG/<br>SWD                     | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | JTAG/<br>SWD                     | MSIO:<br>fabric                  | JTAG/<br>SWD                     | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             |

| Bank 5   | MSIO:<br>fabric                  | DDRIO:<br>FDDR or<br>fabric      | MSIO:<br>fabric                  | JTAG/<br>SWD                     | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | JTAG/<br>SWD                     | DDRIO:<br>FDDR or<br>fabric      | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric            |

| Bank 6   | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | MSIO:<br>fabric                  | -                                | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0<br>or fabric  | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0 or<br>fabric  | MSIOD:<br>fabric                 | MSIOD:<br>fabric                 | MSIO:<br>fabric             |

| Bank 7   | JTAG/<br>SWD                     | MSIOD:<br>fabric                 | MSIOD:<br>fabric                 | MSIOD:<br>SERDES 0<br>or fabric  | JTAG/<br>SWD                     | JTAG/<br>SWD                     | MSIOD:<br>fabric                 | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric                 | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                           |

| Bank 8   | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0<br>or fabric  | MSIO:<br>fabric                  | _                                | MSIO:<br>fabric                  | MSIOD:<br>fabric                 | MSIO:<br>fabric                  | _                                | _                                | -                           |

| Bank 9   | MSIOD:<br>SERDES 3<br>or fabric  | MSIOD:<br>SERDES 1<br>or fabric  | _                                | MSIO:<br>fabric                  | MSIOD:<br>SERDES 3<br>or fabric  | MSIOD:<br>SERDES 3<br>or fabric  | _                                | MSIO:<br>fabric                  | _                                | -                                | _                                | -                           |

| Bank 10  | MSIOD:<br>SERDES 2<br>or fabric  | _                                | _                                | -                                | MSIOD:<br>SERDES 2<br>or fabric  | MSIOD:<br>SERDES 2<br>or fabric  | -                                | _                                | _                                | _                                | _                                | -                           |

#### Table 1 • Organization of I/O Banks in IGLOO2 Devices - FC1152, FCS536, FCV484, FG896, FG676, and FG484

|          | FC1152                           | FC1152 FG896 FG676               |                                  | FCS536                           | FCV484                           | FG484                            |                                  |                                  |                                  |                                  |                                  |          |

|----------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------|

| Bank No. | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL050TS<br>M2GL050T<br>M2GL050 | M2GL090TS<br>M2GL090T<br>M2GL090 | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL150TS<br>M2GL150T<br>M2GL150 | M2GL090TS<br>M2GL090T<br>M2GL090 | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL050TS<br>M2GL050T<br>M2GL050 | M2GL025TS<br>M2GL050T<br>M2GL025 | M2GL010TS<br>M2GL010T<br>M2GL010 | M2GL005S |

| Bank 11  | MSIO:<br>fabric                  | -                                | -                                | -                                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                                | -                                | _                                | -                                | -                                | -        |

| Bank 12  | MSIOD:<br>SERDES 1<br>or fabric  | _                                | _                                | -                                | MSIOD:<br>SERDES 1 or<br>fabric  | MSIOD:<br>SERDES 1<br>or fabric  | -                                | _                                | _                                | -                                | _                                | -        |

| Bank 13  | MSIOD:<br>SERDES 0<br>or fabric  | _                                | _                                | -                                | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | -                                | _                                | _                                | -                                | _                                | -        |

| Bank 14  | MSIO:<br>fabric                  | _                                | _                                | -                                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                                | -                                | _                                | -                                | _                                | -        |

| Bank 15  | MSIOD:<br>fabric                 | _                                | _                                | -                                | MSIOD:<br>fabric                 | _                                | _                                | _                                | -                                | -                                | -                                | -        |

| Bank 16  | MSIOD:<br>fabric                 | _                                | _                                | -                                | MSIOD:<br>fabric                 | MSIOD:<br>fabric                 | _                                | _                                | _                                | -                                | _                                | -        |

| Bank 17  | MSIO:<br>fabric                  | _                                | -                                | -                                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | _                                | _                                | -                                | -                                | -                                | -        |

| Bank 18  | MSIO:<br>fabric                  | -                                | -                                | -                                | MSIO:<br>fabric                  | -                                | _                                | _                                | -                                | -                                | -                                | _        |

| Note: Ba | anks that are s                  | shaded should                    | d always be po                   | owered with th                   | ne appropriate V                 | DDI bank sup                     | plies.                           | I                                |                                  | I                                |                                  | L        |

#### Table 1 • Organization of I/O Banks in IGLOO2 Devices - FC1152, FCS536, FCV484, FG896, FG676, and FG484 (continued)

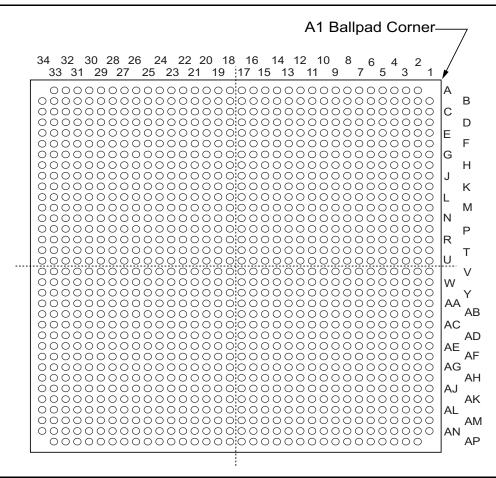

|          | VF400                            |                                  |                                  |                                  |                             | FCS325                           |                                  |                                                                                              | VF256                            |                                  |                                  | TQ144            |                  |                  |

|----------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-----------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------|------------------|------------------|------------------|

| Bank No. | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL050TS<br>M2GL050T<br>M2GL050 | M2GL025TS<br>M2GL025T<br>M2GL025 | M2GL010TS<br>M2GL010T<br>M2GL010 | M2GL005S                    | M2GL090TS<br>M2GL090T<br>M2GL090 | M2GL060TS<br>M2GL060T<br>M2GL060 | M2GL050TS<br>M2GL050T<br>M2GL050                                                             | M2GL025TS<br>M2GL025T<br>M2GL025 | M2GL025TS<br>M2GL025T<br>M2GL025 | M2GL010TS<br>M2GL010T<br>M2GL010 | M2GL005S         | M2GL010          | M2GL005S         |

| Bank 0   | -                                | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric | -                                | _                                | DDRIO:<br>MDDR or<br>fabric                                                                  | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>fabric | DDRIO:<br>fabric | DDRIO:<br>fabric |

| Bank 1   | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             | DDRIO:<br>MDDR or<br>fabric      | DDRIO:<br>MDDR or<br>fabric      | MSIO:<br>fabric                                                                              | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric  | -                | -                |

| Bank 2   | MSIO:<br>fabric                  | -                                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                                                                              | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric  | MSIO:<br>fabric  | MSIO:<br>fabric  |

| Bank 3   |                                  | MSIO:<br>fabric                  | JTAG/<br>SWD                     | JTAG/<br>SWD                     | JTAG/<br>SWD                | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                                                                              | JTAG/<br>SWD                     | JTAG/<br>SWD                     | JTAG/<br>SWD                     | JTAG/<br>SWD     | JTAG/<br>SWD     | JTAG/<br>SWD     |

| Bank 4   | MSIO:<br>fabric                  | JTAG/<br>SWD                     | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric             | JTAG/<br>SWD                     | MSIO:<br>fabric                  | JTAG/<br>SWD                                                                                 | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric  | MSIO:<br>fabric  | MSIO:<br>fabric  |

| Bank 5   | JTAG/<br>SWD                     | DDRIO:<br>FDDR or<br>fabric      | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric            | MSIO:<br>fabric                  | JTAG/<br>SWD                     | DDRIO:<br>FDDR or<br>fabric                                                                  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric | _                | MSIOD:<br>fabric |

| Bank 6   | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric                 | MSIOD:<br>fabric                 | MSIO:<br>fabric             | MSIOD:<br>SERDES 0<br>or fabric  | MSIO:<br>fabric                  | MSIOD:<br>SERDES 0<br>or fabric                                                              | MSIO:<br>fabric                  | MSIOD:<br>fabric                 | MSIOD:<br>fabric                 | MSIO:<br>fabric  | MSIOD:<br>fabric | MSIO:<br>fabric  |

| Bank 7   | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric                 | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                           | MSIOD:<br>fabric                 | MSIOD:<br>SERDES 0<br>or fabric  | MSIOD:<br>fabric                                                                             | MSIO:<br>fabric                  | MSIO:<br>fabric                  | MSIO:<br>fabric                  | -                | MSIO:<br>fabric  | -                |

| Bank 8   | MSIOD:<br>fabric                 | MSIO:<br>fabric                  | _                                | -                                | _                           | MSIO:<br>fabric                  | MSIOD:<br>fabric                 | MSIO:<br>fabric                                                                              | _                                | _                                | _                                | _                | _                | _                |

| Bank 9   | MSIO:<br>fabric                  | _                                | _                                | _                                | _                           | _                                | MSIO: fabric                     | _                                                                                            | _                                | -                                | -                                | _                | -                | _                |

|          | fabric                           |                                  | d alwa                           |                                  |                             |                                  |                                  | -     -     -     MSIO: fabric       ays be powered with the appropriate VDDI bank supplies. |                                  |                                  |                                  |                  |                  |                  |

#### Table 2 • Organization of I/O Banks in IGLOO2 Devices - VF400, FCS325, VF256, and TQ144

#### Table 3 • User I/O Types

| Name                                                                                                                                                                                                           | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MSIOxyBz                                                                                                                                                                                                       | In/out | MSIOs provide programmable drive strength, weak pull-up, and weak-pull-down.<br>In single-ended mode, the I/O pair operates as two separate I/Os named P and N. IGLOO2 I/O<br>ports also support ESD protection. MSIO I/O cells operate at up to 3.3 V and are capable of<br>high-speed LVDS2V5 and LVDS3V3 operation.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| MSIODxyBz                                                                                                                                                                                                      | In/out | MSIOD is very similar to MSIO, but drops 3.3 V and hot-plug support and adds pre-emphasis, in order to achieve higher speeds. MSIODs provide programmable drive strength, weak pull-up, and weak pull-down. MSIOD I/O cells operate at up to 2.5 V and are capable of high-speed LVDS2V5 operation. Some of these pins are also multiplexed with the SERDES interface. IGLOO2 I/O ports support ESD protection.                                                                                                                                                                                                                                                                        |  |  |  |  |

| DDRIOxyBz                                                                                                                                                                                                      | In/out | The double data input output (DDRIO) is a multi-standard I/O optimized for LPDDR/DDR2/DDR3 performance. In IGLOO2 devices there are two DDR subsystems: the fabric DDR and High Performance Memory Subsystem (HPMS) DDR controllers. All DDRIOs can be configured as differential I/Os or two single-ended I/Os. If you select MDDR/FDDR, Libero <sup>®</sup> System-on-Chip (SoC) automatically connects MDDR/FDDR signals to the DDRIOs. DDRIOs can be connected to the respective DDR subsystem PHYs or can be used as user I/Os. Depending on the memory configuration, only the required DDRIOs are used by Libero SoC. The unused DDRIOs are available to connect to the fabric. |  |  |  |  |

| Note: For more information on I/O status of MSIO, MSIOD and DDRIO pins during power up/down and default conditions, refer to AC396: SmartFusion2 and IGLOO2 in Hot Swapping and Cold Sparing Application Note. |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

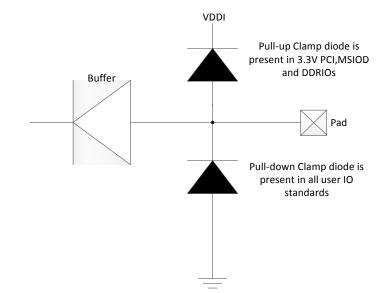

All user IOs have internal clamp diode control circuitry. A pull-up clamp diode must not be present in the I/O circuitry if the hot-swap feature is used. The 3.3 V PCI standard requires a pull-up clamp diode on the I/O, so it cannot be selected if hot-swap capability is required.

Figure 27 • Internal Clamp Diode Control Circuitry

## **Naming Conventions**

### **User I/O Naming Conventions**

The naming convention used for each FPGA user I/O is IOxyBz, where:

IO is the type of I/O—MSIO, MSIOD, or DDRIO.

x refers the I/O pair number in bank z.

**y** is P (positive) or N (negative). In single-ended mode, the I/O pair operates as two separate I/Os named P and N. Differential mode is implemented with a fixed I/O pair and cannot be split with an adjacent I/O.

B is bank.

z refers to bank number (0-9 for M2GL050-FG896).

Differential standards are implemented as true differential outputs and complementary single-ended outputs for SSTL/HSTL. In the single-ended mode, the I/O pair operates as two separate I/Os named P and N. All the configuration and data inputs/outputs are then separate and use names ending in P and N to differentiate between the two I/Os.

For more information, refer to the "I/Os" chapter of the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

### **Dedicated Global I/O Naming Conventions**

Dedicated global I/Os are dual-use I/Os which can drive the global blocks either directly or through clock conditioning circuits (CCC) or virtual clock conditioning circuits (VCCC). They can also be used as regular user I/Os. These global I/Os are the primary source for bringing in the external clock inputs into the IGLOO2 device.

In the M2GL050T-FG896 device, there are 16 global blocks located in the center of the fabric and 32 global I/Os located 8 each on the north, east, south, and west sides of the fabric. There are 6 CCC blocks, located 2 each on northwest, northeast, and southwest side of the fabric and 2 VCCC blocks on the southeast side of the fabric.

Dedicated global I/Os that drive the global blocks (GB) directly are named as GBn, where

**n** is 0 to 15.

Dedicated global I/Os that drive GBs through CCCs are named as CCC\_xyz\_CLKIw, where:

xy is the location-NE, SW, or NW.

**z** is 0 or 1.

I represents input clock

${\bf w}$  refers to one of the four possible output clocks of the associated CCC\_xyz—GL0, GL1, GL2, or GL3.

Dedicated global I/Os that drive GBs through VCCCs are named as VCCC\_SEz, where:

SE is southeast.

**z** is 0 or 1.

Unused dedicated global I/Os behave similarly to unused regular User I/Os (MSIO, MSIOD, DDRIO). Libero configures unused User I/Os as input buffer disabled, output buffer tristated with weak pull-up.

For further details, refer to the "Fabric Global Routing Resources" chapter of the UG0449: SmartFusion2 SoC FPGA and IGLOO2 FPGA Clocking Resources User Guide.

## **MDDR/FDDR Interface**

IGLOO2 devices have MDDR/FDDR blocks. The DDR subsystems are hardened ASIC blocks for interfacing the LPDDR, DDR2, and DDR3 memories. It supports 8-/16-/32-bit data bus width modes. The DDRIO uses fixed impedance calibration for different drive strengths. These values can be programmed using Libero SoC software for the selected I/O standard. The values are fed to the pull-up/pull-down reference network to match the impedance with an external resistor. For more information about reference resistor values (for different drive modes), refer to the *UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide*.

### **DDR Controller Pins**

Table 4 shows the DDR Controller pins.

| Table 4 • | DDR | Controller | Pins |

|-----------|-----|------------|------|

|-----------|-----|------------|------|

| Pin Name                  | Туре   | Reference Resistor (Ω)                                                                                            |

|---------------------------|--------|-------------------------------------------------------------------------------------------------------------------|

| xDDR_CAS_N                | Out    | DRAM CASN.                                                                                                        |

| xDDR_CKE                  | Out    | DRAM Clock enable.                                                                                                |

| xDDR_CLK                  | Out    | DRAM single-ended clock for differential pads.                                                                    |

| xDDR_CLK_N                | Out    | DRAM single-ended clock for differential pads.                                                                    |

| xDDR_CS_N                 | Out    | DRAM Chip select.                                                                                                 |

| xDDR_ODT                  | Out    | DRAM on-die termination (ODT). 0: Termination OFF                                                                 |

|                           |        | 1: Termination ON                                                                                                 |

| xDDR_RAS_N                | Out    | DRAMRASN                                                                                                          |

| xDDR_RESET_N              | Out    | DRAM reset for DDR3                                                                                               |

| xDDR_WE_N                 | Out    | DRAM Write enable                                                                                                 |

| xDDR_ADDR[15:0]           | Out    | DRAM address bits.                                                                                                |

| xDDR_BA[2:0]              | Out    | DRAM bank address.                                                                                                |

| xDDR_DM_RDQS[3:0]         | In/out | DRAM data mask from bidirectional pads.                                                                           |

| xDDR_DQS[3:0]             | In/out | DRAM single-ended data strobe output for bidirectional pads.                                                      |

| xDDR_DQS[3:0]_N           | In/out | DRAM single-ended data strobe output for bidirectional pads.                                                      |

| xDDR_DQ[31:0]             | In/out | DRAM data input or output for bidirectional pads.                                                                 |

| xDDR_DQ_ECC[3:0]          | In/out | DRAM data input or output for SECDED.                                                                             |

| xDDR_DM_RDQS_ECC          | In/out | DRAM single-ended data strobe output for bidirectional pads.                                                      |

| xDDR_DQS_ECC              | In/out | DRAM single-ended data strobe output for bidirectional pads.                                                      |

| xDDR_DQS_ECC_N            | In/out | DRAM data input or output for bidirectional pads.                                                                 |

| xDDR_TMATCH_[0/1]_IN      | In     | DQS enable input for timing match between DQS and system clock.<br>For simulations, tie to xDDR_TMATCH_[0/1]_OUT. |

| xDDR_TMATCH_[0/1]_O<br>UT | Out    | DQS enable output for timing match between DQS and system clock.<br>For simulations, tie to xDDR_TMATCH_[0/1]_IN. |

| xDDR_TMATCH_ECC_IN        | In     | DQS enable input for timing match between DQS and system clock.<br>For simulations, tie to xDDR_TMATCH_ECC_OUT.   |

Notes:

1. Though calibration is not required, it is recommended to use corresponding resistor placeholder to connect the xDDR\_IMP\_CALIB to the ground with or without a resistor.

2. x represents Fabric or MSS DDR.

#### Table 4 • DDR Controller Pins (continued)

| xDDR_TMATCH_ECC_O<br>UT | Out | DQS enable output for timing match between DQS and system clock. For simulations, tie to xDDR_TMATCH_ECC_IN.                                          |

|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| xDDR_IMP_CALIB          | Ref | <ul> <li>Pull-down with resistor depending on voltage/standard:</li> <li>DDR2 - 150 Ω</li> <li>DDR3 (1.5 V) - 240 Ω</li> <li>LPDDR - 150 Ω</li> </ul> |

Notes:

1. Though calibration is not required, it is recommended to use corresponding resistor placeholder to connect the xDDR\_IMP\_CALIB to the ground with or without a resistor.

2. x represents Fabric or MSS DDR.

For more information about DDR memory calibration, refer to the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

For DDR termination details refer AC393: SmartFusion2 and IGLOO2 Board Design Guidelines Application Note.

### I/O Standards

Table 5 shows the supported I/O standards for different DDR memories.

#### Table 5 • Supported I/O Standards for Different DDR Memories

| Memory Type | I/O Standard      |

|-------------|-------------------|

| DDR3        | SSTL15I, SSTL15II |

| DDR2        | SSTL18I, SSTL18II |

| LPDDR       | LVCMOS18          |

## **Supply Pins**

IGLOO2 devices support multi-standard I/Os (MSIOs), MSIODs, double data rate I/Os (DDRIOs), high performance memory subsystem (HPMS), high speed serial interfaces, and a debugging JTAG interface. IGLOO2 devices require the power supplies listed in Table 6.

#### Table 6 • Supply Pins

| Name               | Туре                             | Description                                                                                                                                             |

|--------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                | Supply                           | DC core supply voltage. Must always power this pin.                                                                                                     |

| VPP                | Supply <sup>1</sup>              | Power supply for charge pumps (for normal operation and programming). Must always power this pin.                                                       |

| VPPNVM             | Supply <sup>1</sup>              | Analog sense circuit supply of embedded nonvolatile memory (eNVM). Must be shorted to VPP.                                                              |

| VDDIx              | Bank power supplies <sup>2</sup> | VDDIx, Bank x power                                                                                                                                     |

| VREFx              | Supply <sup>3</sup>              | Reference voltage for MDDR signals which is powered through corresponding Bank Supply (VDDIx). When <b>unused</b> , VREFx can be DNC or grounded (VSS). |

| CCC_NE0_PLL_VDDA   | PLL power                        | Analog power pad for PLL0                                                                                                                               |

| CCC_NE1_PLL_VDDA   | supplies <sup>4</sup>            | Analog power pad for PLL1                                                                                                                               |

| CCC_NW0_PLL_VDDA   |                                  | Analog power pad for PLL2                                                                                                                               |

| CCC_NW1_PLL_VDDA   |                                  | Analog power pad for PLL3                                                                                                                               |

| CCC_SW0_PLL_VDDA   |                                  | Analog power pad for PLL4                                                                                                                               |

| CCC_SW1_PLL_VDDA   |                                  | Analog power pad for PLL5                                                                                                                               |

| HPMS_MDDR_PLL_VDDA |                                  | Analog power pad for PLL of MDDR and HPMS                                                                                                               |

| FDDR_PLL_VDDA      |                                  | Analog power pad for PLL of FDDR                                                                                                                        |

Notes:

1. For details on VPP and VPPNVM power supplies, refer to Table 2 - Recommended Operating Conditions of the DS0128: IGLO02 FPGA and SmartFusion2 SoC FPGA Datasheet.

- For details on bank power supplies, refer to the "Recommendation for Unused Bank Supplies" table in the AC393: SmartFusion2 and IGLOO2 Board Design Guidelines Application Note. For more details on user I/O pins (MSIO, MSIOD, DDRIO) and supported voltage standards, refer to the Supported Voltage Standards table in the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

- 3. Reference voltages should be powered with the appropriate bank supplies through voltage divider circuitry. If I/O banks are being used as single-ended I/Os (and MDDR or FDDR functionalities are not being used), then VREFx can be left floating (DNC) even though the VDDIx powered to the corresponding supplies.

- 4. If used as PLL, the supply must be connected over resistor and capacitors (filter circuitry) to a common PLL supply (2.5 V or 3.3 V) to the corresponding on-board PLL return path. If PLL is unused or used as divider, the supply must connect directly to either 2.5 V or 3.3 V (without filter circuitry).

- 5. If used, all SERDES PLL pins must be powered through resistor and capacitors (filter circuitry) to the correct appropriate supply to the corresponding on-board return path. If **unused**, must connect directly to the appropriate supplies (without filter circuitry).

- 6. If used, all CCC PLL pins must be powered through resistor and capacitors (filter circuitry) to the appropriate supply to the corresponding on-board return path. If unused must connect directly to the Ground (without filter circuitry).

#### Table 6 • Supply Pins (continued)

| Name                 | Туре                        | Description                                                                                                                                                                   |

|----------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERDES_X_VDD         | SERDESx                     | PCIe/PCS supply. It is a +1.2 V supply and internally shorted to VDD.                                                                                                         |

| SERDES_x_L01_VDDAIO  | power supplies <sup>5</sup> | Tx/Rx analog I/O voltage. Low voltage power for Lane0 and Lane1 of SERDESIFx, located on the left side. It is a +1.2 V SERDES PMA supply.                                     |

| SERDES_x_L23_VDDAIO  |                             | Tx/Rx analog I/O voltage. Low voltage power for Lane2 and Lane3 of SERDESIFx, located on the right side. It is a +1.2 V SERDES PMA supply.                                    |

| SERDES_X_L01_VDDAPLL |                             | Analog power for SERDESx PLL of Lane0 and Lane1. In used condition, it must be connected to +2.5 V. In unused condition, it can be connected to either +2.5 V or VDD (1.2 V). |

| SERDES_x_L23_VDDAPLL |                             | Analog power for SERDESx PLL of Lane0 and Lane1. In used condition, it must be connected to +2.5 V. In unused condition, it can be connected to either +2.5 V or VDD (1.2 V). |

| SERDES_X_L01_REFRET  |                             | Local on-chip ground return path for SERDES_x_L01_VDDAPLL for Lane0<br>and Lane1 of SERDESIF0, located on the left side. If unused, it must<br>be grounded (VSS).             |

| SERDES_X_L23_REFRET  |                             | Local on-chip ground return path for SERDES_x_L23_VDDAPLL for Lane2 and Lane3 of SERDESIF0, located on the right side. If unused, it must be grounded (VSS).                  |

| SERDES_X_PLL_VDDA    |                             | High supply voltage for PLL SERDESx. It can be +2.5 V or +3.3 V.                                                                                                              |

| SERDES_X_PLL_VSSA    |                             | VDDA to on-die VSSA high pass filter connection for PLL SERDESx.<br>If unused, it must be grounded (VSS).                                                                     |

| CCC_NE0_PLL_VSSA     | PLL return                  | Return path for corresponding analog PLL VDDA supply. High                                                                                                                    |

| CCC_NE_PLL_VSSA      | paths <sup>6</sup>          | frequency noise should be eliminated by placing the R-C filter circuitry<br>in between VDDA and VSSA pins.                                                                    |

| CCC_NW0_PLL_VSSA     |                             | in between vDDA and vSSA pins.                                                                                                                                                |

| CCC_NW1_PLL_VSSA     |                             |                                                                                                                                                                               |

| CCC_SW0_PLL_VSSA     |                             |                                                                                                                                                                               |

| CCC_SW1_PLL_VSSA     |                             |                                                                                                                                                                               |

| HPMS_MDDR_PLL_VSSA   |                             | Analog ground pad for PLL of MDDR and HPMS                                                                                                                                    |

| FDDR_PLL_VSSA        |                             | Analog ground pad for PLL of FDDR                                                                                                                                             |

Notes:

- For details on bank power supplies, refer to the "Recommendation for Unused Bank Supplies" table in the AC393: SmartFusion2 and IGLOO2 Board Design Guidelines Application Note. For more details on user I/O pins (MSIO, MSIOD, DDRIO) and supported voltage standards, refer to the Supported Voltage Standards table in the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

- Reference voltages should be powered with the appropriate bank supplies through voltage divider circuitry. If I/O banks

are being used as single-ended I/Os (and MDDR or FDDR functionalities are not being used), then VREFx can be left

floating (DNC) even though the VDDIx powered to the corresponding supplies.

- 4. If used as PLL, the supply must be connected over resistor and capacitors (filter circuitry) to a common PLL supply (2.5 V or 3.3 V) to the corresponding on-board PLL return path. If PLL is unused or used as divider, the supply must connect directly to either 2.5 V or 3.3 V (without filter circuitry).

- If used, all SERDES PLL pins must be powered through resistor and capacitors (filter circuitry) to the correct appropriate supply to the corresponding on-board return path. If **unused**, must connect directly to the appropriate supplies (without filter circuitry).

- 6. If used, all CCC PLL pins must be powered through resistor and capacitors (filter circuitry) to the appropriate supply to the corresponding on-board return path. If unused must connect directly to the Ground (without filter circuitry).

<sup>1.</sup> For details on VPP and VPPNVM power supplies, refer to Table 2 - Recommended Operating Conditions of the DS0128: IGLOO2 FPGA and SmartFusion2 SoC FPGA Datasheet.

#### Table 6 • Supply Pins (continued)

| Name   | Туре   | Description                                                         |

|--------|--------|---------------------------------------------------------------------|

| VSS    | Ground | Ground pad for core and I/Os. Must always connect to ground.        |

| VSSNVM |        | Analog sense circuit ground of eNVM. Must always connect to ground. |

Notes:

- 1. For details on VPP and VPPNVM power supplies, refer to Table 2 Recommended Operating Conditions of the DS0128: IGLOO2 FPGA and SmartFusion2 SoC FPGA Datasheet.

- For details on bank power supplies, refer to the "Recommendation for Unused Bank Supplies" table in the AC393: SmartFusion2 and IGLOO2 Board Design Guidelines Application Note. For more details on user I/O pins (MSIO, MSIOD, DDRIO) and supported voltage standards, refer to the Supported Voltage Standards table in the UG0445: IGLOO2 FPGA and SmartFusion2 SoC FPGA Fabric User Guide.

- 3. Reference voltages should be powered with the appropriate bank supplies through voltage divider circuitry. If I/O banks are being used as single-ended I/Os (and MDDR or FDDR functionalities are not being used), then VREFx can be left floating (DNC) even though the VDDIx powered to the corresponding supplies.

- 4. If used as PLL, the supply must be connected over resistor and capacitors (filter circuitry) to a common PLL supply (2.5 V or 3.3 V) to the corresponding on-board PLL return path. If PLL is unused or used as divider, the supply must connect directly to either 2.5 V or 3.3 V (without filter circuitry).

- If used, all SERDES PLL pins must be powered through resistor and capacitors (filter circuitry) to the correct appropriate supply to the corresponding on-board return path. If **unused**, must connect directly to the appropriate supplies (without filter circuitry).

- 6. If used, all CCC PLL pins must be powered through resistor and capacitors (filter circuitry) to the appropriate supply to the corresponding on-board return path. If unused must connect directly to the Ground (without filter circuitry).

### **Additional Notes on Supply Pins**

- 1. As an alternative to leaving unused positive and ground level supplies floating (not connected, open), they can be shorted to VSS on-board. This could be considered a better practice in avionics, so that floating supplies do not pick up charge from radiation.

- 2. For on-board connectivity solutions, refer to the AC393: SmartFusion2 SoC FPGA and IGLOO2 FPGA Board Design Guidelines Application Note.

# **JTAG Pins**

JTAG pins can operate at any voltage—1.2 V / 1.5 V / 1.8 V /2.5 V / 3.3 V (nominal).

Table 7 • JTAG Pin Names and Descriptions

| Name       | Туре | Bus<br>Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAGSEL    | In   | 1           | JTAG controller selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |      |             | JTAGSEL should be pulled high to JTAG bank supply (VDDI) through 1 $\ensuremath{\kappa\Omega}$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| JTAG_TCK   | In   | 1           | Test clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |      |             | Serial input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/pull-down resistor. If JTAG is not used, Microsemi recommends tying it off.                                                                                                                                                                                                                                                                                                                                                   |

|            |      |             | Connect TCK to GND or +3.3 V through a resistor placed close to the FPGA pin. This prevents totem-pole current on the input buffer and operation in case TMS enters an undesired state.                                                                                                                                                                                                                                                                                                                                          |

|            |      |             | Note: To operate at all +3.3 V voltages, 500 $\Omega$ to 1 k $\Omega$ satisfies the requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| JTAG_TDI   | In   | 1           | Test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |      |             | Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.                                                                                                                                                                                                                                                                                                                                                                                                            |

| JTAG_TDO   | Out  | 1           | Test data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |      |             | Serial output for JTAG boundary scan, ISP, and UJTAG usage. The TDO pin does not have an internal pull-up/-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                        |

| JTAG_TMS   | -    | 1           | Test mode select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |      |             | The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, and TRST). There is an internal weak pull-up resistor on the TMS pin.                                                                                                                                                                                                                                                                                                                                                                            |

| JTAG_TRSTB | -    | 1           | Boundary scan reset pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |      |             | The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor (1 k) could be included to ensure the TAP is held in Reset mode. In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends that you tie off TRST to GND through a resistor (1 k) placed close to the FPGA pin. |

# **Programming SPI**

The system controller contains a dedicated SPI block for programming. The SPI is operated in either Master or Slave mode. In Master mode, the IGLOO2 device is interfaced with an external SPI flash device and the programming data is downloaded from it to the FPGA. In Slave mode, it is communicated with a remote device that initiates download of the programming data to the FPGA.

Table 8 • Programming SPI Interface

| Name           | Туре | Description                                                                                                                                                                                                                                                         |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC_SPI_SS      | Out  | SPI slave select                                                                                                                                                                                                                                                    |

| SC_SPI_SDO     | Out  | SPI data output                                                                                                                                                                                                                                                     |

| SC_SPI_SDI     | In   | SPI data input                                                                                                                                                                                                                                                      |

| SC_SPI_CLK     | Out  | SPI clock                                                                                                                                                                                                                                                           |

| FLASH_GOLDEN_N | In   | If pulled Low, this indicates that the device is to be re-programmed from an image in the external SPI flash attached to the SPI interface. If pulled High, the SPI is put into slave mode. Add an external pull-up resistor value of 10 k $\Omega$ to VDDI (Bank). |

Notes:

1. If unused, SPI programming pins must be left floating.

2. For more details related to reset, clock, and programming, refer to the AC393: SmartFusion2 SoC FPGA and IGLOO2 FPGA Board Design Guidelines Application Note.

3. For more information on remaining programming modes, refer to the UG0451: SmartFusion2 SoC FPGA and IGLOO2 FPGA Programming User Guide.

# **Dedicated I/Os**

Dedicated I/Os (Table 9 and Table 10 on page 39) can be used for a single purpose such as SERDES, device reset, or clock functions. IGLOO2 dedicated I/Os:

- Device reset pins

- Crystal oscillator pins

- SERDES I/Os

- Programming SPI pins

#### Table 9 • Device Reset and Crystal Oscillator Pin Types and Descriptions

| Pin                                     | Туре  | Description                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Reset I/Os                       |       |                                                                                                                                                                                                                                                                                             |

| DEVRST_n                                | Input | Device reset; active Low and powered by VPP. It is an asynchronous signal and Schmitt trigger input with the maximum slew rate must not exceed 1 $\mu$ s. When DEVRST_n is asserted, all user IOs are fully tri-stated. In unused condition, pull up to VPP through 10 k $\Omega$ resistor. |

| Crystal Oscillator I/Os <sup>1, 2</sup> |       |                                                                                                                                                                                                                                                                                             |

| XTLOSC_MAIN_EXTAL                       | Input | Crystal connection or external RC network.                                                                                                                                                                                                                                                  |

| XTLOSC_MAIN_XTAL                        | Input | Input clock from the main crystal oscillator.                                                                                                                                                                                                                                               |

Notes:

1. The M2GL050 device has only a main crystal oscillator.

2. Crystal oscillator pins have a nominal 50 k $\Omega$  internal weak pull-ups to VPP. If unused, those pins can be left floating (DNC). The pins should not be grounded (VSS).

# **SERDES I/Os**

The SERDES I/Os available in IGLOO2 devices are dedicated for high speed serial communication protocols. The SERDES I/Os support protocols such as PCI Express 2.0, XAUI, serial gigabit media independent interface (SGMII), serial rapid IO (SRIO), and any user-defined high speed serial protocol implementation in fabric. Refer to the *AC393: SmartFusion2 SoC FPGA and IGLOO2 FPGA Board Design Guidelines Application Note* for further information.

| Port Name              | Туре                                 | Description                                                                                                                                                  |  |  |  |  |

|------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data / Reference Pads  | Data / Reference Pads                |                                                                                                                                                              |  |  |  |  |

| SERDES_X_RXD0_P        |                                      | Receive data. SERDES differential positive input for each lane.                                                                                              |  |  |  |  |

| SERDES_x_RXD1_P        | Input <sup>1</sup>                   | Each SERDESIF consists of 4 RX signals. Here $x = 0$ for SERDESIF_0 and $x = 1$ for SERDESIF 1.                                                              |  |  |  |  |

| SERDES_X_RXD2_P        | input                                |                                                                                                                                                              |  |  |  |  |

| SERDES_X_RXD3_P        |                                      |                                                                                                                                                              |  |  |  |  |

| SERDES_X_RXD0_N        |                                      | Receive data. SERDES differential negative input for each lane.                                                                                              |  |  |  |  |

| SERDES_X_RXD1_N        | Input <sup>1</sup>                   | Each SERDESIF consists of 4 RX signals. Here $x = 0$ for SERDESIF_0 and $x = 1$ for SERDESIF 1                                                               |  |  |  |  |

| SERDES_X_RXD2_N        | input                                | x - I IUI SERDESIF_I                                                                                                                                         |  |  |  |  |

| SERDES_X_RXD3_N        |                                      |                                                                                                                                                              |  |  |  |  |

| SERDES_X_TXD0_P        |                                      | Transmit data. SERDES differential positive output for each lane.                                                                                            |  |  |  |  |

| SERDES_x_TXD1_P        | Output <sup>2</sup>                  | Each SERDESIF consists of 4 TX signals. Here $x = 0$ for SERDESIF_0 and $y = 1$ for SERDESIE 1                                                               |  |  |  |  |

| SERDES_X_TXD2_P        | Output                               | x = 1 for SERDESIF_1.                                                                                                                                        |  |  |  |  |

| SERDES_x_TXD3_P        |                                      |                                                                                                                                                              |  |  |  |  |

| SERDES_X_TXD0_N        |                                      | Transmit data. SERDES differential negative output for each lane.                                                                                            |  |  |  |  |

| SERDES_x_TXD1_N        | Output <sup>2</sup>                  | Each SERDESIF consists of 4 TX signals. Here x = 0 for SERDESIF_0 and x = 1 for SERDESIF_1.                                                                  |  |  |  |  |

| SERDES_X_TXD2_N        | Output                               |                                                                                                                                                              |  |  |  |  |

| SERDES_X_TXD3_N        |                                      |                                                                                                                                                              |  |  |  |  |

| Common I/O Pads per SE | Common I/O Pads per SERDES Interface |                                                                                                                                                              |  |  |  |  |

| SERDES_x_L01_REXT      |                                      | External reference resistor connection to calibrate TX/RX termination value.                                                                                 |  |  |  |  |

| SERDES_X_L23_REXT      | Reference <sup>2</sup>               | Each SERDESIF consists of 2 REXT signals—one for Lane0 and Lane1, and another for Lane2 and Lane3. Here $x = 0$ for SERDESIF_0 and $x = 1$ for SERDESIF_1.   |  |  |  |  |

| SERDES_X_REFCLK0_P     | <b>e</b> t 13                        | Reference clock differential positive. Each SERDESIF consists of two signals (REFCLK0_P, REFCLK1_P). Here $x = 0$ for SERDESIF_0 and $x = 1$ for SERDESIF_1. |  |  |  |  |

| SERDES_X_REFCLK1_P     | Clock <sup>3</sup>                   |                                                                                                                                                              |  |  |  |  |

| SERDES_X_REFCLK0_N     | 01.13                                | Reference clock differential negative. Each SERDESIF consists of two                                                                                         |  |  |  |  |

| SERDES_X_REFCLK1_N     | Clock <sup>3</sup>                   | signals (REFCLK0_P, REFCLK1_P). Here x = 0 for SERDESIF_0 and x = 1 for SERDESIF_1.                                                                          |  |  |  |  |

Notes:

1. If unused, must always connect to VSS (ground).

2. If the SERDES unit is not being used, these pins must remain floating (DNC).

3. These pins are MUXed with MSIOD functionality. If SERDES functionality and MSIOD functionality are not used, the pins must be left floating. Libero SoC will disable unused I/Os and weakly pull them up.

# **Special Pins**

The two live probe I/O cells are dual-purpose. If live probe functionality will never be used on these I/Os, the user can configure the I/O as an input, output, or bidirectional. However, if the intent is to perform live switching between the user I/O and probe functionality, then use the I/O only as an output. If it were configured as an input during general use, then as soon as it is switched over to live probe operation, the probe circuitry would drive out onto this I/O, potentially causing device damage.

Table 11 • Special Pins

| Name                  | Туре   | Description                                                                                                                                                                                |

|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROBE_A               | In/out | The two live probe I/O cells are dual-purpose:                                                                                                                                             |

| PROBE_B               | In/out | 1. Live probe functionality                                                                                                                                                                |

|                       |        | 2. User I/O                                                                                                                                                                                |

| CCC_xyz_CLKI0         | Input  | Input clock from dedicated input pad 0. The xy portion refers to the CCC location (NE, SW, SE, or NW) and z represents the CCC number (0 or 1).                                            |

| CCC_xyz_CLKI1         | Input  | Input clock from dedicated input pad 1. The xy portion refers to the CCC location (NE, SW, SE, or NW) and z represents the CCC number (0 or 1).                                            |

| CCC_xyz_CLKI2         | Input  | Input clock from dedicated input pad 2. The xy portion refers to the CCC location (NE, SW, SE, or NW) and z represents the CCC number (0 or 1).                                            |

| CCC_xyz_CLKI3         | Input  | Input clock from dedicated input pad 3. The xy portion refers to the CCC location (NE, SW, SE, or NW) and z represents the CCC number (0 or 1).                                            |

| GBx                   | Input  | GB is a multiplexer that generates an independent global signal. The GBs can be driven from multiple sources such as dedicated global I/Os, fabric CCCs, VCCCs, and fabric routing         |

| xDDR_TMATCH_[0/1]_IN  | Input  | DQS enable input for timing match between DQS and system clock.<br>TMATCH_IN and TMATCH_OUT pins need to be looped back with the trace<br>length as short as possible.                     |