# **ZSC31150 Functional Description**

# **Contents**

| 1 | Con  | ntrol | Logic                                                                     | 4  |

|---|------|-------|---------------------------------------------------------------------------|----|

|   | 1.1. | Ge    | neral Description                                                         | 4  |

|   | 1.2. | CIV   | C Description                                                             | 4  |

|   | 1.3. | Ge    | neral Working Modes                                                       | 4  |

|   | 1.3. | 1.    | Normal Operation Mode (NOM)                                               | 4  |

|   | 1.3. | 2.    | Command Mode (CM)                                                         | 5  |

|   | 1.3. | 3.    | Diagnostic Mode (DM), Failsafe Tasks, and Error Codes                     | 5  |

| 2 | Sigr | nal ( | Conditioning                                                              | 8  |

|   | 2.1. |       | Conversion                                                                |    |

|   | 2.2. | ΑD    | Conversion Result Segmentation                                            | 9  |

|   | 2.3. | _     | nal Conditioning Formula                                                  |    |

|   | 2.4. | Ana   | alog and Digital Output                                                   | 11 |

|   | 2.5. | _     | ital Filter Function                                                      |    |

|   | 2.6. |       | tput Signal Range and Limitation                                          |    |

| 3 |      |       | Digital Interface (SIF)                                                   |    |

|   | 3.1. | Ge    | neral Description                                                         |    |

|   | 3.1. | 1.    | Addressing                                                                |    |

|   | 3.1. | 2.    | Communication Verification                                                |    |

|   | 3.1. | ٠.    |                                                                           |    |

|   |      |       | Protocol                                                                  |    |

|   | 3.3. | _     | ital One-Wire Interface (OWI)                                             |    |

| 4 |      |       | e Commands                                                                |    |

|   | 4.1. |       | mmand Set                                                                 |    |

|   | 4.2. |       | mmand Processing                                                          |    |

|   | 4.3. |       | Output Registers                                                          |    |

|   | 4.4. |       | mmand Response Codes                                                      |    |

|   | 4.5. |       | ailed Description for Specific Commands                                   |    |

|   |      |       | START_CM (72D1 <sub>HEX</sub> )                                           |    |

|   |      |       | START_AD_CNT (62 <sub>HEX</sub> )                                         |    |

|   | 4.5. |       | ADJ_OSC_ACQ (50 <sub>HEX</sub> ) and ADJ_OSC_WRI (65xxxx <sub>HEX</sub> ) |    |

| 5 |      |       | M and RAM                                                                 |    |

|   | 5.1. |       | gramming the EEPROM                                                       |    |

|   | 5.2. |       | PROM and RAM Content                                                      |    |

|   | 5.2. |       | Traceability                                                              |    |

|   | 5.2. |       | Configuration Words                                                       |    |

|   | 5.3. |       | PROM Signature                                                            |    |

| _ | 5.4. |       | PROM Write Locking                                                        |    |

| 6 |      | •     | rature Sensor Adaption and CMV Measurement                                |    |

|   | 6.1. |       | mperature Measurement when Sensor Bridge is in Voltage Excitation Mode    |    |

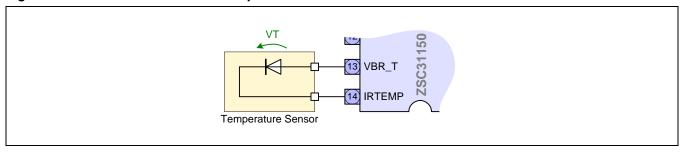

|   | 6.1. |       | Internal PN-Junction TS                                                   |    |

|   | 6.1. |       | External PN-Junction TS                                                   |    |

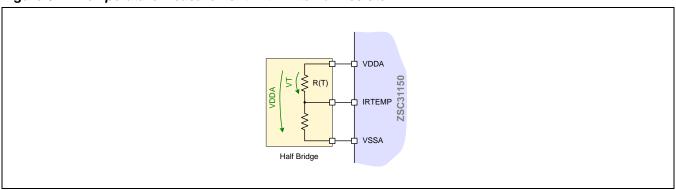

|   | 6.1. | პ.    | External Resistor                                                         | 38 |

| 6.1.4.     | Result and Sensitivity Calculation                                   | 38 |

|------------|----------------------------------------------------------------------|----|

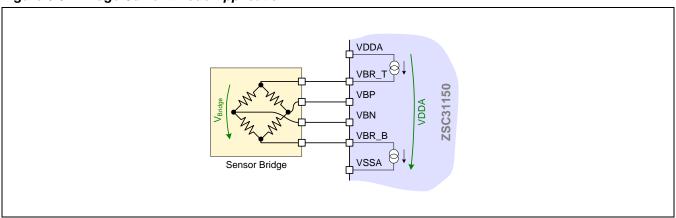

| 6.2. Te    | emperature Measurement when Sensor Bridge in Current Excitation Mode |    |

| 6.3. CI    | MV Measurement                                                       | 39 |

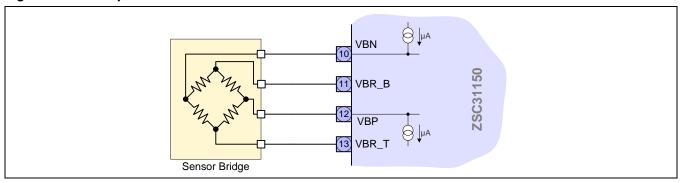

| 6.4. Se    | ensor Check                                                          | 40 |

| 7 Relate   | d Documents                                                          | 41 |

| 8 Glossa   | ary                                                                  | 42 |

| 9 Docum    | nent Revision History                                                | 43 |

|            |                                                                      |    |

|            |                                                                      |    |

|            |                                                                      |    |

| List of I  | Figures                                                              |    |

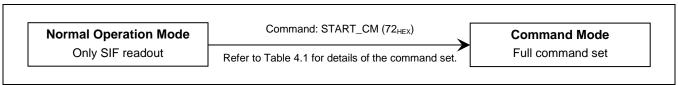

| Figure 1.1 | Modes of Digital Serial Communication                                | 5  |

| Figure 2.1 | Accessible Output Signal Range and Limitation                        | 12 |

| Figure 3.1 | I <sup>2</sup> C – Principles of Protocol                            | 14 |

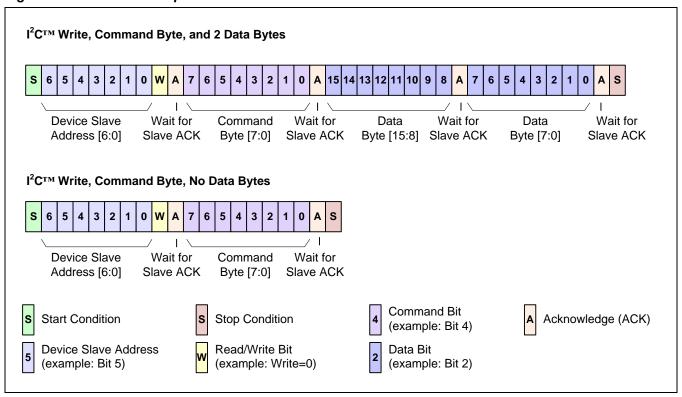

| Figure 3.2 | I <sup>2</sup> C™ – Write Operation                                  | 15 |

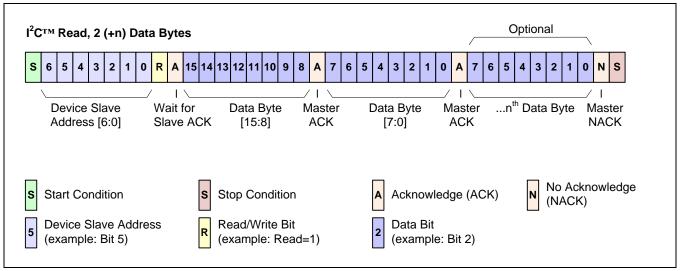

| Figure 3.3 | I <sup>2</sup> C™ – Read Operation – Data Request                    | 16 |

| Figure 3.4 | I <sup>2</sup> C™ – Timing Protocol                                  | 17 |

| Figure 3.5 | Block Diagram of the OWI Connection                                  | 18 |

| Figure 3.6 | OWI - Stop Condition for Active Driven AOUT                          | 19 |

| Figure 3.7 | OWI – Write Operation                                                | 20 |

| Figure 3.8 | OWI - Read Operation - Data Request                                  | 21 |

| Figure 3.9 | OWI – Timing Protocol                                                | 21 |

| Figure 4.1 | Preventing Misinterpretation of Check Sum                            | 25 |

| Figure 4.2 | START_CM Command                                                     | 26 |

| Figure 5.1 | Source-Code Signature Generation                                     | 35 |

| Figure 6.1 | External PN-Junction Temperature Sensor                              | 37 |

| Figure 6.2 | Temperature Measurement with External Resistor                       | 38 |

| Figure 6.3 | Bridge Current Mode Application                                      | 39 |

| Figure 6.4 | Principle of Sensor Short Check                                      | 41 |

# **List of Tables**

| Table 1.1 | Error Codes                                                                          | 7  |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 2.1 | Valid Data Ranges for 15-bit and 16-bit ADC Resolution                               | 9  |

| Table 3.1 | Timing I <sup>2</sup> C Protocol                                                     | 17 |

| Table 3.2 | OWI Interface Parameters                                                             | 19 |

| Table 3.3 | OWI Timing Protocol                                                                  | 21 |

| Table 4.1 | Command Set                                                                          | 22 |

| Table 4.2 | Output Register Contents of Serial Digital Interface (SIF) When Processing Commands  | 25 |

| Table 4.3 | Command Response: First Readout Word (SIF Output Register 1)                         | 26 |

| Table 4.4 | START_AD_CNT - Data Word Description                                                 | 27 |

| Table 4.5 | START_AD_CNT - Command Response Description                                          | 28 |

| Table 4.6 | Oscillator Frequency Adjustment Sequence / Tasks (OWI Only)                          | 28 |

| Table 5.1 | EEPROM and RAM Content                                                               | 30 |

| Table 5.2 | Lot, Wafer, x-Position, and y-Position Number Calculation Procedure                  | 31 |

| Table 5.3 | Configuration Word CFGAFE                                                            | 32 |

| Table 5.4 | Configuration Word CFGAPP                                                            | 33 |

| Table 5.5 | Configuration Word ADJREF                                                            | 34 |

| Table 5.6 | Configuration Word RESERVED                                                          | 34 |

| Table 6.1 | Configuration Temperature Measurement                                                | 36 |

| Table 6.2 | Sensitivity Internal Temperature Sensor                                              | 36 |

| Table 6.3 | Sensitivity and IRTEMP Input Signal Range in mV/V using External PN-Junction Mode    | 37 |

| Table 6.4 | Temperature Measurement Input Range Midpoint in mV (RM <sub>ED</sub> )               | 37 |

| Table 6.5 | ZSC31150 Input Signal Range for External Resistor Mode (Voltages referenced to VDDA) | 38 |

| Table 6.6 | Temperature Gain Coefficients                                                        | 38 |

| Table 6.7 | Temperature Measurement in Bridge Current Excitation Mode (CFGAPP:CSBE=1)            | 39 |

# 1 Control Logic

## 1.1. General Description

The control logic of the ZSC31150 consists of the calibration microcontroller (CMC) and the control logic modules of the analog-to-digital (A/D) converter and serial digital interface. The configuration of the various modes of the device is done by programming an EEPROM.

The CMC controls the measurement cycle and performs the calculations for sensor signal conditioning. This eliminates the gain deviation, the offset, the temperature deviation, and the non-linearity of the pre-amplified and A/D-converted sensor signal.

Communication between the ZSC31150 and an external microcontroller, especially for calibration purposes, is done via a serial digital interface. Communication protocols according to the I²C standard are supported. A one-wire interface called OWI with the brand name ZACwire™ is also implemented. These serial interfaces are used for calibration of the sensor system consisting of a sensor transducer and the ZSC31150. The serial interface provides the read-out of the results of sensor signal conditioning as digital values during the calibration. The internal processing of received interface commands is done by the CMC. Therefore, the measurement cycle is interrupted if a command is received. Only the read-out of data is controlled by the serial interface itself and does not interrupt the CMC.

The controller of the A/D conversion is started by the CMC and executed as a continuous measurement cycle. The conditioning calculation by the CMC works in parallel to the A/D conversion.

# 1.2. CMC Description

The CMC is especially adapted to the tasks connected with the signal conditioning.

The main features are

- 16-bit processing width and programming via ROM.

- Constants/coefficients for the conditioning calculation stored in the EEPROM. After power-on or after re-initialization from EEPROM by sending a specific command to the serial interface, the EEPROM is mirrored to the RAM.

- Continuous parity checking during every read from RAM. If incorrect data is detected, the diagnostic mode (DM) is activated (an error code is written to the serial digital output; the analog out is set to the diagnostic level).

# 1.3. General Working Modes

The ZSC31150 supports three different working modes:

- Normal Operation Mode (NOM)

- Command Mode (CM)

- Diagnostic Mode (DM)

The command set includes commands for changing the working mode. Refer to section 4 for a detailed description of these commands.

#### 1.3.1. Normal Operation Mode (NOM)

The NOM is the recommended working mode for applications. After power-on, the ZSC31150 starts with an initialization routine, and the NOM will be activated after this.

During the initialization routine, first the EEPROM is mirrored to the RAM, which checks the EEPROM content. If an error is detected, the DM is activated. The configuration of the ZSC31150, which is stored in the EEPROM, is consecutively set.

Next, the continuous measurement cycle and the conditioning calculation start. The signal conditioning result is refreshed with each cycle time period. This generates the analog output at the AOUT pin, and it can be read via the serial digital Interface (SIF) as a digital output.

Provided that the EEPROM is programmed correctly, the NOM works without the microcontroller sending any command to the digital serial interface. Read-out of the conditioning result via the SIF is possible; this does not interrupt continuous processing of the signal conditioning routine.

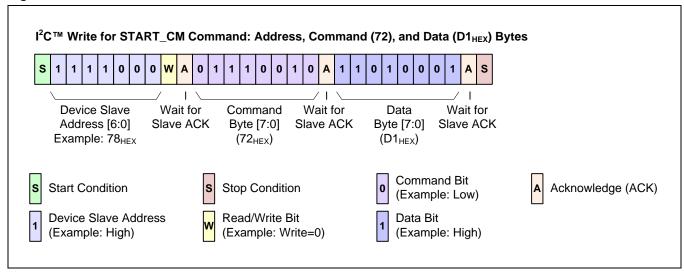

# 1.3.2. Command Mode (CM)

The CM is the working mode that is used for calibration data acquisition and access to the internal RAM and EEPROM of the ZSC31150. The CM start command START\_CM aborts the running NOM, so the measurement cycle is stopped. The ZSC31150 changes to CM only after receiving the START\_CM command via the digital serial interface. This protects the ZSC31150 against interruption of processing during the NOM (= continuous signal conditioning) and/or unintentional changes of configuration. In CM, the full set of commands is supported.

If the ZSC31150 receives a command other than START\_CM in NOM, it is not valid. It will be ignored, and no interrupt to the continuous measurement cycle will be generated. Refer to section 4.5.1 for a detailed description of the START\_CM command.

In CM, the full command set is enabled for processing. During processing of a received command, the serial interface is disabled, and no further commands are recognized. After finishing the routine, the CMC waits for further commands or the process loops continuously (e.g., after measurement commands).

Figure 1.1 Modes of Digital Serial Communication

EEPROM programming is only enabled after receiving the EEP WRITE EN command.

Starting CM via I<sup>2</sup>C communication (SCL and SDA pins) is possible at any time. For communication via the one-wire interface (AOUT pin), several modes can be activated in the configuration setup, e.g., the start window.

# 1.3.3. Diagnostic Mode (DM), Failsafe Tasks, and Error Codes

The ZSC31150 detects various possible failures, in which case the DM is activated. The DM is indicated by the ZSC31150 setting the output pin AOUT in the lower diagnostic range (LDR) and the output registers of the digital serial interface are set to a defined error code. In this case, independent from configuration, the OWI and  $I^2$ C communication is enabled, and an error code can be read out.

Because the analog output AOUT is driven LOW, the AOUT pin must be overwritten (AOUT current limitation: < 20mA) for starting digital communication using the OWI interface. Therefore the communication master must provide driving capability for doing this.

Note that the error detection functionality can be partly enabled/disabled by configuration words (e.g., sensor connection check, sensor aging (CMV) limits, ROM check, etc.).

The failure counting sequence/procedure is called the "Temporary DM." The DM (LDR) will be activated after two sequential detected failure events and will be deactivated after counting down the failure counter if the failure condition is no longer given.

#### 1.3.3.1. Power and Ground Loss

Power and ground loss cases are indicated by pulling the AOUT pin into the lower or upper diagnostic range (LDR/UDR) in the event of a lost node or load connection to ground or the supply. The ZSC31150 is inactive in this case, and the specified leakage current in combination with the load resistor guarantees reaching the LDR or UDR.

# 1.3.3.2. Temperature Sensor Check \*

The temperature sensor check monitors whether the ADC exceeds lower or upper temperature limits. Possible causes of failure are

- The external temperature sensor is unconnected.

- The offset of the temperature measurement (ADJREF:TOFFS) is not sufficiently adjusted; signal is out of the ADC range.

The temperature raw value (T) is checked to determine if it is equal 0 or if it is greater or equal to (2<sup>RESOLUTION</sup> - 1). 16/15 bit raw values are shifted to 14/13 bits before the check. The temperature sensor (TS) check uses the failure counter sequence (i.e., temporary DM).

<sup>\*</sup> **Note:** The Temperature Sensor Check is only available for ZSC31150<u>D</u>xx and subsequent versions.

# Table 1.1 Error Codes

**Note:** In the case of detection of different failures with the code " $C0xx_{HEX}$ ," the codes are "OR" combined. If any signature or configuration error occurs, it is overwritten if there is a watchdog error at the watchdog timeout.

| Failsafe Task                                                                   | Description                                                                                                                             | Messaging Time                 | Error Code          | Deactivation | Action                                  |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------|--------------|-----------------------------------------|--|

| Oscillator Fail (OFC)                                                           | Detects faulty oscillator operation                                                                                                     | < 200µs                        | -                   | No           | Temporary<br>DM                         |  |

| Watchdog Timeout (WDG)                                                          | Detection of watchdog timeout of start routine (69632 clocks) or measurement cycle (2 x conversion cycle time)                          | Always                         | C008 <sub>HEX</sub> | No           | DM or Reset                             |  |

| RAM Parity (RAP)                                                                | Parity check at every RAM access                                                                                                        | Without Delay                  | C001 <sub>HEX</sub> | No           | DM or Reset                             |  |

| Register Parity (RGP)                                                           | Permanent parity check of configuration registers                                                                                       | Without Delay                  | C002 <sub>HEX</sub> | No           | DM or Reset                             |  |

| EEPROM Multi-bit<br>(EMC)                                                       | Detection of non-correctable multi-<br>bit error per 16-bit word                                                                        | Start Up                       | C004 <sub>HEX</sub> | No           | DM                                      |  |

| EEPROM Signature (ECS)                                                          | Signature check during read out of EEPROM after power-on or after START_CYC_EEP* command                                                | Start Up                       | C0AA <sub>HEX</sub> | No           | DM                                      |  |

| ROM Signature (RSC)                                                             | ROM signature check at power-on (enabled by CFGAPP:CHKROM; needs approximately 10ms additional startup time)                            | Start Up                       | COCC <sub>HEX</sub> | Yes          | DM                                      |  |

| Only for product codes ZSC31150Ex and earlier: Inconsistent Configuration (ICC) | Detects digital averaging filter coefficients failure, analog output limits out of addressable range, or undefined command in CM        | Start Up /<br>Command Received | C0FF <sub>HEX</sub> | No           | DM                                      |  |

| Arithmetic Check (ACC)                                                          | Functional check of arithmetic unit during measurement cycle                                                                            |                                | C010 <sub>HEX</sub> | No           | DM or Reset                             |  |

| SCC                                                                             | Sensor connection check (enabled by CFGAPP:CHKSENS)                                                                                     |                                | C010 <sub>HEX</sub> | Yes          |                                         |  |

| Temperature Sensor (TS) Check                                                   | Temperature sensor AD conversion result check = 0 <sub>HEX</sub> or (2 <sup>RESOLUTION</sup> – 1)                                       | Processed once per             | C010 <sub>HEX</sub> | Yes          | Temporary                               |  |

| SSC (P/N)                                                                       | SSC (P/N)  Sensor short check positive/negative biased (enabled by CFGAPP:CHKSENS)                                                      |                                | C010 <sub>HEX</sub> | Yes          | DM<br>(temporary<br>diagnostic<br>mode) |  |

| Sensor Aging (CMV)                                                              | Compares sensor bridge common mode voltage to programmed limits Disabled by register A <sub>HEX</sub> = FF00 <sub>HEX</sub>             |                                | C010 <sub>HEX</sub> | Yes          | ŕ                                       |  |

| Power & Ground<br>Loss (PGL)                                                    | Power and ground loss detection; in<br>the event of PGL, the output is<br>pulled into the LDR or UDR by an<br>external pull-up resistor | <5ms                           | -                   | No           | Reset                                   |  |

# 2 Signal Conditioning

### 2.1. AD Conversion

During NOM, the analog preconditioned sensor signal is continuously converted by the ADC. The A/D conversion is configurable for resolution  $r_{ADC}$  and the inherent range shift RS<sub>ADC</sub> by the configuration word CFGAFE (see Table 5.3). The one or two step conversion mode is selectable. The two-step mode is faster; the one-step mode is more accurate because of the longer integration time. The selected resolution for the A/D conversion is equal for all measurements in the measurement cycle (e.g., input voltage, temperature, auto-zero, etc.). The resulting digital raw values for the measured value (e.g., pressure) and temperature are determined by the following equations:

#### ⇒ Analog differential input voltage to A/D conversion

Measured value V<sub>IN DIFF</sub> to be conditioned:

$$V_{ADC\_DIFF} = a_{IN} * V_{IN\_DIFF} + a_{XZC} * V_{XZC}$$

⇒ Digital raw A/D conversion result:

$$Z_{ADC} = 2^{r_{ADC}} \left( \frac{V_{ADC\_DIFF} + V_{OFF}}{V_{ADC\_REF}} + 1 - RS_{ADC} \right)$$

⇒ Auto-zero value:

$$Z_{AZ} = 2^{r_{ADC}} \left( \frac{V_{OFF}}{V_{ADC\_REF}} + 1 - RS_{ADC} \right)$$

⇒ Auto-zero corrected raw A/D conversion result:

$$Z_{\text{CORR}} = Z_{\text{ADC}} - Z_{\text{AZ}} = 2^{r_{\text{ADC}}} \left( \frac{V_{\text{ADC\_DIFF}}}{V_{\text{ADC\_REF}}} \right)$$

| $V_{IN\_DIFF}$   | Differential voltage input to analog front-end                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| $V_{OFF}$        | Residual offset voltage of analog front-end (which is eliminated by $Z_{\text{ADC}}-Z_{\text{AZ}}$ difference calculation)     |

| $V_{XZC}$        | Extended zero compensation voltage (refer to the ZSC31150 Data Sheet for details):                                             |

|                  | $V_{XZC} = V_{ADC\_REF} * PXZC \left( \frac{(3^{PXZCPOL} - 2)}{48} \right)$                                                    |

|                  | (PXZC and PXZCPOL are bit fields in register CFGAFE.)                                                                          |

| a <sub>IN</sub>  | Gain of analog front-end for differential input voltage (see Table 5.3)                                                        |

| a <sub>XZC</sub> | Gain of extended zero compensation voltage (refer to the ZSC31150 Data Sheet for details)                                      |

| $V_{ADC\_DIFF}$  | Differential input voltage to A/D converter                                                                                    |

| $V_{ADC\_REF}$   | ADC reference voltage (ratiometric reference for measurement)                                                                  |

| r <sub>ADC</sub> | Resolution of A/D conversion                                                                                                   |

| $RS_ADC$         | Range shift of A/D conversion:<br>Bridge Sensor Measurement: ½, ¾, <sup>7</sup> / <sub>8</sub> , <sup>15</sup> / <sub>16</sub> |

Temperature Measurement: ½ (see section 6)

# 2.2. AD Conversion Result Segmentation

The result of the AD conversion  $Z_{CORR}$ , which is the input value for the signal conditioning formula, depends on the resolution adjustment  $r_{ADC}$  ranging from 13 to 16 bit resolution. Raw values acquired with resolutions of 15 and 16 bits must be mapped to the 13 or 14 bit resolution range for further calculations. This is done by different methods depending on the data to be measured:

- CMV, SSC+, and SSC- measurements for diagnostic checks are always shifted to 13 bits.

- The temperature measurement data (Z<sub>CORR T</sub>) are divided by 4.

- The bridge sensor (BR) measurement auto-zero corrected data (Z<sub>CORR</sub>) must be moved in the +/- 2<sup>15</sup> range (see Table 2.1) by subtraction of the offset determined in configuration register CFGAPP:POFFS (see Table 5.4). Minimum and maximum input data (span of Z<sub>CORR</sub> raw data) should have 14-bit or slightly higher resolution (16384 ADC counts) for proper calibration coefficients calculation.

### AD conversion result segmentation calculation (only if $r_{ADC} = 15$ or 16 bit)

$$Z_{CORR\_OUT} = Z_{CORR} - POFFS * 2^{13} \\ \text{with POFFS} \in [0; 7] \\ Z_{CORR\_TOUT} = \frac{Z_{CORR\_T}}{4} \\ \\ Z_{CORR\_TOUT} = \frac{Z_{CORR\_T}}{4} \\ \\ Z_{CORR\_TOUT} = \frac{Z_{CORR\_T}}{4} \\ \\ Z_{CORR\_TOUT} \\ \\ Z_{CORR\_TOU$$

**Note:** All raw data acquiring commands (Dx commands listed in Table 4.1) do not process the shifting procedure, and therefore 15 and 16 bit results are read out. Therefore the acquired data must be processed according to the  $Z_{CORR\_OUT}$  and  $Z_{CORR\_TOUT}$  formulas above in the following sequence before calculation of the calibration coefficients:

- 1. Raw calibration data acquisition

- 2. Z<sub>CORR OUT</sub> calculation for the main channel data and the Z<sub>CORR T</sub> calculation for temperature data

- 3. Calibration coefficients calculation using calculated corrected raw data

**Important:** Results of the ADC conversion  $Z_{CORR\_OUT}$  greater than +32767 counts (15 bits) will result in negative read-out values and a wrong analog output voltage for AOUT. In this case, a greater offset POFFS, adjusted ADC Range Shift, or lower gain should be used.

Table 2.1 Valid Data Ranges for 15-bit and 16-bit ADC Resolution

| ADC        | Range Shift                                                           | 1/2    |       | 3/4    |       | 7/8   |       | 15/16 |       |

|------------|-----------------------------------------------------------------------|--------|-------|--------|-------|-------|-------|-------|-------|

| Resolution | Data                                                                  | Min    | Max   | Min    | Max   | Min   | Max   | Min   | Max   |

| 16 bits    | Z <sub>CORR_IN</sub> (D8 <sub>HEX</sub> & D9 <sub>HEX</sub> commands) | -32768 | 32767 | -16384 | 49151 | -8192 | 57343 | -4096 | 61439 |

| 15 bits    |                                                                       | -16384 | 16383 | -8192  | 24575 | -4096 | 28671 | -2048 | 30719 |

| 16 bits    | Z <sub>CORR_OUT</sub>                                                 | -32768 | 32767 | -16384 | 32767 | -8192 | 32767 | -4096 | 32767 |

| 15 bits    |                                                                       | -16384 | 16383 | -8192  | 24575 | -4096 | 28671 | -2048 | 30719 |

**Recommendation:** To avoid possible ADC saturation, perform a check on the ADC raw data (D0<sub>HEX</sub> and D1<sub>HEX</sub> commands). For results close to the limits [0-2<sup>res</sup>), a lower gain or adjusted RangeShift should be used.

# 2.3. Signal Conditioning Formula

The digital raw value  $Z_{CORR}$  for the measured value to be conditioned is further processed with the correction formula to remove offset and temperature dependency and to compensate non-linearity up to  $3^{rd}$  order. The signal conditioning equation is computed by the CMC and is defined as follows:

# ⇒ Range definition of inputs

$$\begin{split} &Z_{CORR} \in \left[ -2^{r_{ADC}}; 2^{r_{ADC}} \right) \\ &Z_{CORR\_T} \in \left[ -2^{r_{ADC}-1}; 2^{r_{ADC}-1} \right) \end{split}$$

# ⇒ Conditioning equations (P = Bridge Sensor Measurand)

$$Y = \frac{Z_{CORR} + c_0 + 2^{-(r_{ADC} - 1)} * c_4 * Z_{CORR\_T} + 2^{-2(r_{ADC} - 1)} * c_5 * Z_{CORR\_T}^2}{c_1 + 2^{-(r_{ADC} - 1)} * c_6 * Z_{CORR\_T} + 2^{-2(r_{ADC} - 1)} * c_7 * Z_{CORR\_T}^2}$$

$$Y \in [0; 1)$$

$$P = Y \Big( 1 - 2^{-15} * c_2 - 2^{-15} * c_3 \Big) + 2^{-15} * c_2 * Y^2 + 2^{-15} * c_3 * Y^3$$

$$P \in [0; 1)$$

Conditioning coefficients stored in EEPROM registers 0 to 7

$$c_i \in [-2^{15}; 2^{15})$$

, two's complement

The first equation calculates the intermediate result Y for compensating the offset and fitting the gain including its temperature dependence. The non-linearity is corrected in the next equation, which calculates the non-negative value P for the measured bridge sensor value in the range [0;1). This value P is continuously written to the output register of the digital serial interface during the measurement cycle.

**Note:** The conditioning coefficients c<sub>i</sub> are positive or negative values in two's complement format.

# 2.4. Analog and Digital Output

The DAC used for generation of the analog output has 5632 levels.

**Important:** To fit the normalized conditioning result P [0;1) to the DAC ranges, the targets for calibration must be multiplied by  $0.6875 = \binom{5632}{2^{13}}$ .

If using the calibration library *RBIC1.DLL*: Note that this multiplication is done in the ZSC31150 Evaluation Kit Software and is not contained in *RBIC1.DLL*. Refer to the *Calibration DLL Description (RBIC\_DLL\_description.txt)* for a description of stand-alone usage of the DLL. *RBIC1.DLL* and *RBIC\_DLL\_description.txt* can be found in the in the program folder on the user's PC after installation of the ZSC31150 Evaluation Software.

The digital output, i.e., the conditioning result readable via the SIF, is calculated with 15-bit resolution/accuracy (maximum). The MSB is used as the error identifier – if the MSB is set, an error is indicated. In normal cases, this means that if the targets are adjusted for using analog output, the digital output is weighted with factor 0.6875.

If only digital output is used, targets can be calculated using the full 15-bit resolution/accuracy range. The ZSC31150 Evaluation Kit Software offers the option for doing this.

# 2.5. Digital Filter Function

The ZSC31150 offers a digital (averaging) filter function for calculating the output result in NOM. These filters can also be used for acquiring data in calibration procedures using the START\_AD\_CNT command "62."

The filter can be parameterized using two programmable coefficients stored in EEPROM: an integrating coefficient PAVG and a differential coefficient PDIFF. (See Table 5.1.) The output Pout<sub>i</sub> is set to P<sub>i</sub> for the first calculation of an output result for a (new) sent command (e.g., starting NOM or "62").

Set PDIFF and PAVG to 0 to disable the filter function. Default settings for the ZSC31150 disable the filter function. With this function it is possible to build up a low-pass filter.

**Important:** Ensure that the coefficient  $\frac{PDIFF+1}{2^{PAVG}}$  never exceeds 1.

If this coefficient exceeds 1, the filter function can oscillate and the system gets a flywheel effect. The filter function can be described as follows:

#### ⇒ Digital filter function

Pout<sub>i</sub> = Pout<sub>i-1</sub> +

$$\left(P_i - Pout_{i-1} \left(\frac{PDIFF + 1}{2^{PAVG}}\right)\right)$$

: i>0 with PAVG, PDIFF  $\in [0; 7]$

P<sub>i</sub> Conditioning equation result for bridge sensor signal (refer to section 2.2)

Pout<sub>i</sub> Output result to be calculated

PAVG Averaging filter coefficient (EEPROM register 08<sub>HEX</sub>, [2:0])

PDIFF Differential filter coefficient (EEPROM register 09<sub>HEX</sub>, [2:0])

# 2.6. Output Signal Range and Limitation

The bridge sensor measurand conditioning result P for the measured value is output at the analog output pin and SIF with >12-bit resolution. The DAC used for generation of the analog output has 5632 levels, where 5120 levels (from 256 to 5375) can be addressed or voltage output from 4.55% to 95.44% of the supply voltage.

$$V_{OUT\_MIN} = (V_{VDDE} - V_{VSSE}) \frac{256}{5632}$$

$V_{OUT\_MAX} = (V_{VDDE} - V_{VSSE}) \frac{5375}{5632}$

As a result, an adjustable range from 5% to 95% of the supply including all possible tolerances is guaranteed. Setting the analog output outside the allowed range (for example via the Set\_DAC command) will result in entering the diagnostic mode (DM) and setting the output to LDR (Lower Diagnostic Range).

Note that the limit setting registers  $08_{HEX}$  and  $09_{HEX}$  (see Table 5.1) are shared with the digital filter configuration (the 3 LSBs).

Figure 2.1 Accessible Output Signal Range and Limitation

ZSC31150 offers an output limitation function *for the analog output AOUT*, which clips the output signal if the calculated result is outside of the defined limits. These output minimum and maximum limits (13-bit accuracy) are defined in EEPROM.

⇒ Limitation

$$\begin{split} &P_{\text{out}} \left( P > L_{\text{max}} \right) = L_{\text{max}} \\ &P_{\text{out}} \left( P < L_{\text{min}} \right) = L_{\text{min}} \qquad \qquad P_{\text{out}} \in \left[ L_{\text{min}} \, ; \, L_{\text{max}} \, \right] \end{split}$$

Limits stored in bits [15:3] of EEPROM registers 08<sub>HEX</sub> and 09<sub>HEX</sub>:

$\begin{array}{lll} L_{\text{min}} & \text{Lower output limit,} \\ L_{\text{max}} & \text{Upper output limit} \\ \\ L_{\text{min/max}} \in [100_{\text{HEX}};\,14FF_{\text{HEX}}] \text{ or } [256_{\text{DEC}};\,5375_{\text{DEC}}] \end{array}$

The output signal V<sub>OUT</sub> is ratiometric to the power supply (V<sub>VDDE</sub> - V<sub>VSSE</sub>) and can be calculated via this equation:

The digital output signal, which is calculated with 14-bit resolution, can be read out using digital serial interface communication. Refer to section 4.3 for a detailed description of the SIF output registers.

# 3 Serial Digital Interface (SIF)

# 3.1. General Description

The ZSC31150 includes a serial digital interface (SIF), which is able to communicate using two communication protocols: I<sup>2</sup>C and ZACwire<sup>™</sup> one-wire communication (OWI). The SIF allows programming the EEPROM to configure the application mode of the ZSC31150 and to calibrate the conditioning equations. It provides the read out of the conditioning result of the measured value as a digital value. The ZSC31150 always works as a slave.

The communication protocol used is selectable. In Command Mode (CM) both communication protocols are always available. The access mode for OWI communication is programmable in EEPROM (ADJREF: IFOWIM; see Table 5.5). There are two start window modes and a mode with continuous OWI access. OWI access can also be locked so that communication is only possible via the I<sup>2</sup>C protocol.

An unconfigured ZSC31150, identified by a non-consistent EEPROM signature, always starts in diagnostic mode (DM). The output is driven LOW in this case so that the lower diagnostic range can be detected. Independent from the configuration, OWI and I<sup>2</sup>C communication is enabled, any error codes can be read out, and access to the EEPROM content for rewriting is possible.

A command consists of an address byte and a command byte. Some commands (e.g., writing data into EEPROM) also include two data bytes. This is independent of the communication protocol used. Refer to section 1.3 for details about working modes and section 4 for command descriptions.

There are two general types of requests to read data via the SIF from the ZSC31150:

- Continuously reading the conditioning result in NOM

- → Digital data read out

- Reading of internal data (e.g., RAM/EEPROM content) or acquired measurement data in CM

- → Calibration and/or configuration tasks

To read internal and/or measurement data from the ZSC31150 in CM, normally a specific command must be sent to transfer this data into the output register of the SIF. Thereafter the READ command consisting of the address byte with the read bit set is used to retrieve this data. The data transmission is continuously repeated until the master sends a stop condition. Again this is independent of the communication protocol used. During the measurement cycle (NOM), the ZSC31150 transfers the conditioning result into the output register of the SIF. These data will be sent if the master generates a read-request. The active measurement cycle is not interrupted by this.

#### 3.1.1. Addressing

Addressing is supported by the I<sup>2</sup>C and ZACwire<sup>™</sup> interface. Every slave connected to the master responds to a specific address. After generating the start condition, the master sends the address byte containing a 7-bit address followed by a data direction bit (R/W). A '0' indicates a transmission from master to slave (WRITE); a '1' indicates a data request (READ).

The general ZSC31150 slave address is  $78_{\text{HEX}}$  (7-bit). The addressed slave answers with an acknowledge (only I<sup>2</sup>C). All other slaves connected to the master ignore this communication. Via EEPROM programming, it is possible to allocate and activate an additional available slave address within the range  $70_{\text{HEX}}$  to  $7F_{\text{HEX}}$  to a single device. In this case, the device recognizes communication on both addresses, on the general one and on the additional one.

#### 3.1.2. Communication Verification

A read request is answered by the data present in the SIF output registers (2 bytes). A check sum is also sent (1 byte) followed by the command that is being answered. The check sum and the returned command allow the verification of received data by the master. For details and exceptions, also see section 4.3.

#### 3.1.3. Communication Protocol Selection

Both available protocols, I<sup>2</sup>C and OWI, are active in parallel, but only one interface can be used at a time.

OWI communication access is also possible if OWI communication is enabled and the analog output is active (OWIANA and OWIWIN after start window; see section 3.3). For this option, the active output AOUT must be overwritten by the communication master, so it is recommended that a stop condition be generated before starting the communication to guarantee a defined start of communication (refer to section 3.3).

# 3.2. I<sup>2</sup>C Protocol

For I<sup>2</sup>C communication, a data line (SDA) and a clock line (SCL) are required.

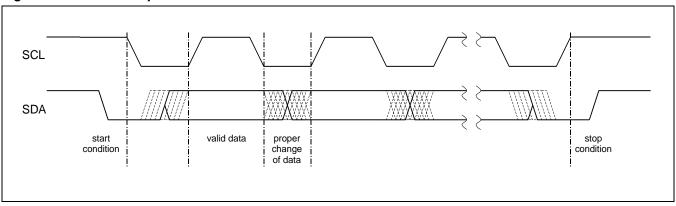

Figure 3.1 C - Principles of Protocol

The I<sup>2</sup>C communication and protocol used is defined as follows:

#### Idle Period

During inactivity of the bus, SDA and SCL are pulled-up to the supply voltage VDDA.

#### Start Condition

A high-to-low transition on SDA while SCL is at the high level indicates a start condition. Every command must be initiated by a start condition sent by a master. A master can always generate a start condition.

#### Stop Condition

A low-to-high transition on SDA while SCL is at the high level indicates a stop condition. A command must be closed by a stop condition to start processing the command routine in the ZSC31150.

#### Valid Data

Data is transmitted in bytes (8 bits) starting with the most significant bit (MSB). Each byte transmitted is followed by an acknowledge bit. Transmitted bits are valid if after a start condition, SDA remains at a constant level during the high period of SCL. The SDA level must change only when the clock signal at SCL is low.

#### Acknowledge

An acknowledge after a transmitted byte is obligatory. The master must generate an acknowledge-related clock pulse. The receiver (slave or master) pulls-down the SDA line during the acknowledge clock pulse. If no acknowledge is generated by the receiver, a transmitting slave will become inactive. A transmitting master can abort the transmission by generating a stop condition and can repeat the command.

A receiving master must signal the end of the transfer to the transmitting slave by not generating an acknowledge-related clock pulse at SCL.

The ZSC31150 as a slave changes to inactive interface mode during processing internal command routines started by a previously sent command.

#### Write Operation

An I²C™ WRITE operation is initiated by the master sending the slave an address byte including a data direction bit set to '0' (WRITE). The address byte is followed by a command byte and depending on the transmitted command, an additional two data bytes (optional). The ZSC31150 internal microcontroller evaluates the received command and processes the related routine. The following figure illustrates a write command with two data bytes and without data bytes. A detailed description of the command set is given in section 4.1.

Figure 3.2 I<sup>2</sup>C<sup>™</sup> – Write Operation

#### Read Operation

After a data request from master to slave by sending an address byte including a data direction bit set to '1' (READ), the slave answers by sending data from the interface output registers. The master must generate the transmission clock on SCL, the acknowledges after each data byte (except after the last one), and the stop condition at the end.

A data request is answered by the ZSC31150's interface module and consequently does not interrupt the current process of the internal microcontroller.

**Note:** The data in the activated registers is sent continuously until a stop condition is detected; after transmitting all available data, the slave starts repeating the data.

Figure 3.3 I<sup>2</sup>C<sup>™</sup> – Read Operation – Data Request

During an active measurement cycle, data is constantly updated with conditioning results. To get other data from the slave (e.g., EEPROM content) typically a specific command must be sent before the data request to initiate the transfer of this data to the interface output registers. This command does interrupt the current process of the internal microprocessor and consequently also interrupts an active measurement cycle.

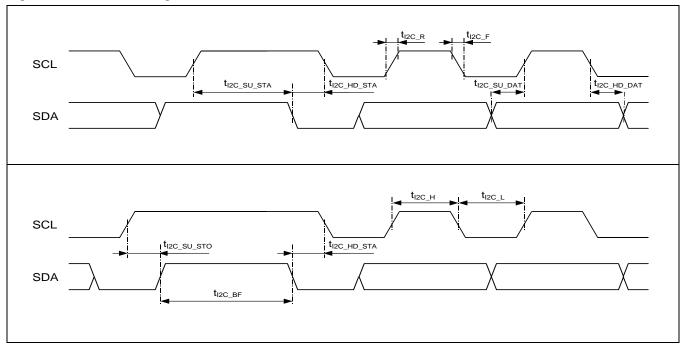

Figure 3.4 I<sup>2</sup>C<sup>™</sup> – Timing Protocol

Table 3.1 Timing I<sup>2</sup>C Protocol

| Nr. | Parameter                                      | Symbol                  | Conditions              | Min | Тур | Max | Unit |

|-----|------------------------------------------------|-------------------------|-------------------------|-----|-----|-----|------|

| 1   | SCL clock frequency                            | f <sub>SCL</sub>        | f <sub>OSC</sub> ≥ 2MHz |     |     | 400 | kHz  |

| 2   | Bus free time between start and stop condition | t <sub>I2C_BF</sub>     |                         | 1.3 |     |     | μS   |

| 3   | Hold time start condition                      | t <sub>I2C_HD_STA</sub> |                         | 0.6 |     |     | μS   |

| 4   | Setup time repeated start condition            | t <sub>I2C_SU_STA</sub> |                         | 0.6 |     |     | μS   |

| 5   | Low period SCL/SDA                             | t <sub>I2C_L</sub>      |                         | 1.3 |     |     | μS   |

| 6   | High period SCL/SDA                            | t <sub>I2C_H</sub>      |                         | 0.6 |     |     | μS   |

| 7   | Data hold time                                 | t <sub>I2C_HD_DAT</sub> |                         | 0   |     |     | μS   |

| 8   | Data setup time                                | t <sub>I2C_SU_DAT</sub> |                         | 0.1 |     |     | μS   |

| 9   | Rise time SCL/SDA                              | t <sub>I2C_R</sub>      |                         |     |     | 0.3 | μS   |

| 10  | Fall time SCL/SDA                              | t <sub>I2C_F</sub>      |                         |     |     | 0.3 | μS   |

| 11  | Setup time stop condition                      | t <sub>I2C_SU_STO</sub> |                         | 0.6 |     |     | μS   |

| 12  | Noise interception SDA/SCL                     | t <sub>I2C_NI</sub>     | Spike suppression       |     |     | 50  | ns   |

Note: See section 1.4 of the ZSC31150 for additional specifications related to the I<sup>2</sup>C interface.

# 3.3. Digital One-Wire Interface (OWI)

The ZSC31150 employs IDT's ZACwire<sup>TM</sup>, a one-wire digital interface concept (OWI). It combines a simple and easy protocol adaptation with a cost-saving pin sharing. The communication principle of the OWI interface is derived from the I<sup>2</sup>C protocol. Becoming familiar with the I<sup>2</sup>C protocol is recommended for an understanding of OWI communication.

Both the analog voltage output and the digital interface (calibration and/or digital output value) use the same pin, AOUT. An advantage of OWI output signal capability is that it enables "end of line" calibration – no additional pins are required to digitally calibrate a finished assembly. However, although the OWI was designed mainly for calibration, it can also be used to digitally read out the calibrated sensor signal continuously.

These two communication tasks are supported by different configurations of the interface. Depending on the EEPROM configuration (ADJREF:IFOWIM, see Table 5.5), there are 4 different modes for OWI:

#### OWIENA → OWI enabled

OWI remains active at the AOUT pin; analog output is disabled. (Note: no internal pull-up resistor is implemented.)

#### OWIWIN → OWI startup window

OWI is enabled during the startup window (~100ms minimum) and is disabled if the startup window times out without receiving a valid START\_CM command [72D1<sub>HEX</sub>]. Analog voltage output is activated after the startup window elapses. (Note: no internal pull-up resistor is implemented).

#### OWIANA → OWI startup window with Analog Out

Analog voltage output is activated after startup time (maximum 5ms). OWI is enabled during the startup window ( $\sim$ 100ms minimum) and is disabled if the startup window times out without receiving a valid START\_CM command [72D1<sub>HEX</sub>]. When sending the START\_CM command, the master must overwrite the active analog voltage output ( $I_{OUT}$  max = 20mA).

#### OWIDIS → OWI disabled

OWI communication is not possible. Access to the ZSC31150 is only available via the I<sup>2</sup>C interface.

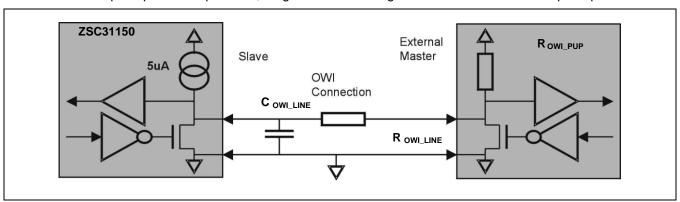

Figure 3.5 Block Diagram of the OWI Connection

Note: An external pull-up must be provided; no guarantee for usage of the ZSC31150 internal pull-up.

In Command Mode (CM), communication via OWI is possible if OWI is enabled. Typically the ZSC31150 is in the OWIENA mode. After specific commands requesting an analog output at the AOUT pin, the mode is comparable to OWIANA but without a timeout.

Both devices are peers; however only the external device starts communication and requests data. In this sense, it is referred to as the master and the ZSC31150 as slave.

In the case of an invalid EEPROM signature, the lower diagnostic range (LDR) driven at the analog output AOUT pin must be overwritten (I<sub>OUT</sub> max=20mA) for sending the START\_CM command. A push-pull driver is necessary for this. It is possible to overwrite the driven analog output AOUT by a communication sequence if OWI is enabled (refer to the OWI modes described above).

#### 3.3.1.1. Properties and Parameters

Although the OWI is designed as a bilateral connection, for reasons of compatibility, the protocol used is equivalent to I<sup>2</sup>C communication. This means a command always includes an address byte with a read/write bit. OWI communication is self-locking (synchronizing) on the master's communication speed within the range specified for OWI bit time, which is guaranteed for ZSC31150's clock frequency in the range of 2 to 4 MHz.

The OWI communication start window in OWIANA and OWIWIN mode is 52700 internal frequency clocks long (~100ms minimum). To initiate OWI communication and enter the Command Mode, the START\_CM command must be sent during this period.

Table 3.2 OWI Interface Parameters

| Nr.   | Parameter                                                                                               | Symbol                | Conditions                                                           | Min  | Max  | Unit |  |  |

|-------|---------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|------|------|------|--|--|

| 1     | OWI bit time 1)                                                                                         | t <sub>OWI_BIT</sub>  | t <sub>BIT</sub> = 10 * R <sub>OWI_PUP</sub> * C <sub>OWI_LOAD</sub> | 0.04 | 4    | ms   |  |  |

| 2     | Pull-up resistance – master                                                                             | R <sub>OWI_PUP</sub>  |                                                                      | 0.3  | 3.30 | kΩ   |  |  |

| 3     | OWI line resistance                                                                                     | R <sub>OWI_LINE</sub> | R <sub>OWI_LINE</sub> < R <sub>OWI_PUP</sub> /100                    | 20   | 33   | Ω    |  |  |

| 4     | OWI load capacitance                                                                                    | C <sub>OWI_LOAD</sub> | Total OWI line load                                                  |      | 50   | nF   |  |  |

| 5     | Voltage level low                                                                                       | $V_{OWI\_IN\_L}$      | Minimum VDDA is 4.2V @ 4.5V VDDE                                     |      | 0.2  | VDDA |  |  |

| 6     | Voltage level high                                                                                      | $V_{OWI\_IN\_H}$      | Maximum VDDA is 5.5V @ 5.5V VDDE                                     | 0.75 |      | VDDA |  |  |

| 1) Ra | Range is guaranteed independent of the clock frequency adjustment. Also see Table 3.3 for more details. |                       |                                                                      |      |      |      |  |  |

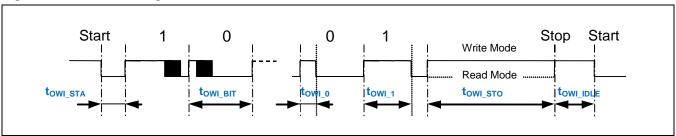

The OWI communication and protocol used is defined as follows:

#### Idle Period

During inactivity of the bus, the OWI communication line is pulled-up to the supply voltage VDDA.

## Start Condition

When the OWI communication line is in idle mode, a low pulse (return to one) with a minimum t<sub>OWI\_STA</sub> width of 25µs indicates a start condition. Every command must be initiated by a start condition sent by a master. A master can generate a start condition only when the OWI line is in the idle mode.

#### Stop Condition

The master finishes a transmission by changing back to the high level (idle mode). Every command (see the following "Write Operation" section for details) must be closed by a stop condition in order to start processing the command. The master can interrupt a transmitting slave after a data request (refer to "Read Operation" below) by clamping the OWI line to the low level for generating a stop condition.

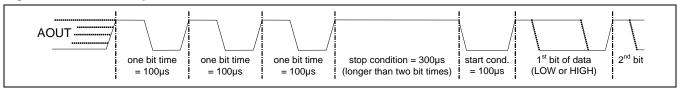

A stop condition is indicated by no transition from low to high or from high to low (constant level) at the OWI line for at least twice the period of the last transmitted valid bit or more than the doubled bit time. A stop condition without regard to the last bit-time (secure stop condition) is generated by a constant level at the OWI line for more than 32766 clocks of the internal clock oscillator. A secure stop condition is also generated at bit times less than 80 clocks of the clock oscillator.

In the case of overwriting an active AOUT (e.g., upon starting communication in OWIANA mode), a stop condition must be generated independently from the current AOUT potential, which can be LOW or HIGH. The timing patterns shown in Figure 3.6 ensure proper generation of the stop condition:

Figure 3.6 OWI – Stop Condition for Active Driven AOUT

#### Valid Data

Data is transmitted in bytes (8 bits) starting with the most significant bit (MSB). Transmitted bits are recognized after a start condition at every transition from low to high on the OWI line. The value of the transmitted bit depends on the duty ratio between the high phase and high/low period (bit period, t<sub>OWI\_BIT</sub>; see Table 3.3). A duty ratio greater than 1/8 and less than 3/8 is detected as a 0; a duty ratio greater than 5/8 and less than 7/8 is detected as a 1.

The bit period of consecutive bits must not change by more than a factor of 2 because a stop condition is detected in this case.

#### Write Operation

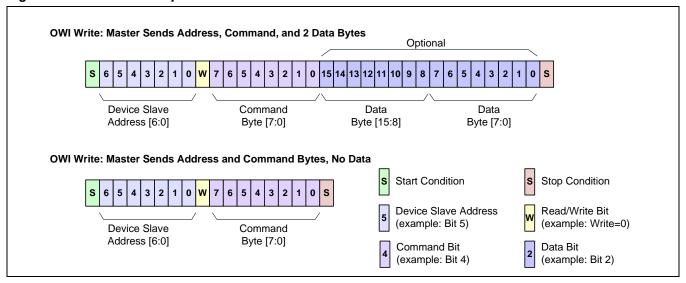

An OWI WRITE operation is initiated by the master sending the slave an address byte including a data direction bit set to 0 (WRITE). The address byte is followed by a command byte and depending on the transmitted command, an additional two data bytes (optional). The ZSC31150 internal microcontroller evaluates the command received and processes the related routine. Figure 3.7 illustrates the write of a command with two data bytes and without data bytes. A detailed description of the command set is given in section 4.1.

Figure 3.7 OWI - Write Operation

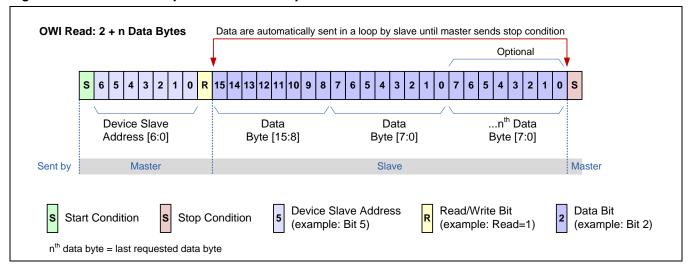

#### Read Operation

After a data request from the master to a slave by sending an address byte including a data direction bit set to 1 (READ), the slave answers by sending data from the interface output registers. The slave generates the data bits with a bit period equal to the last received bit (R/W bit). The master must generate a stop condition after receiving the requested data.

A data request is answered by the ZSC31150's interface module, so it does not interrupt the current process of the internal microcontroller.

The data in the output registers is sent continuously until a stop condition is detected; after transmitting all available data, the slave starts repeating the data.

During the active measurement cycle, data is constantly updated with conditioning results. To get other data from the slave (e.g., EEPROM content) normally a specific command must be sent before the data request to initiate the transfer of this data to the interface output registers. This command does interrupt the present operation of the internal microcontroller and consequently also interrupts any active measurement cycle.

Figure 3.8 OWI - Read Operation - Data Request

Figure 3.9 OWI - Timing Protocol

Table 3.3 OWI Timing Protocol

| Nr. | Parameter                    | Symbol                   | Conditions                                                                                                                               | Min   | Тур  | Max   | Unit                   |

|-----|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------------|

| 1   | Bus free time                | t <sub>OWI_IDLE</sub>    | Between start and stop                                                                                                                   | 25    |      |       | μS                     |

| 2   | Hold time start condition 1) | t <sub>OWI_STA</sub>     |                                                                                                                                          | 25    |      |       | μS                     |

| 3   | Bit period range 2)          | t <sub>OWI_BIT</sub>     | f <sub>OSC</sub> = 4MHz (min.); 2MHz (max.)                                                                                              | 20    |      | 8000  | μS                     |

| 4   | Duty ratio bit '0'           | t <sub>OWI_0</sub>       |                                                                                                                                          | 0.125 | 0.25 | 0.375 | t <sub>OWI_BIT</sub>   |

| 5   | Duty ratio bit '1'           | t <sub>OWI_1</sub>       |                                                                                                                                          | 0.625 | 0.75 | 0.875 | t <sub>OWI_BIT</sub>   |

| 6   | Hold time stop condition     | t <sub>OWI_STO</sub>     | Minimum t <sub>OWI_BIT</sub> (20ms) to bit<br>period of last valid bit<br>(Also see "Stop Condition" on<br>page 19 for further details.) | 2.0   |      |       | t <sub>OWI_BIT_L</sub> |

| 7   | Bit period deviation         | t <sub>OWI_BIT_DEV</sub> | Current bit to next bit                                                                                                                  | 0.55  | 1.0  | 1.5   | t <sub>OWI_BIT</sub>   |

<sup>1)</sup> This hold time is valid for all frequency adjustments for the ZSC31150.

This bit period range is achievable with different frequency adjustments. OWI communication is always possible in the OWI bit time specified in Table 3.2.

# 4 Interface Commands

### 4.1. Command Set

All commands are only available in Command Mode (CM) (see section 1.3.2) and for  $I^2C$  and OWI communication. CM is initiated by sending the START\_CM command [72D1<sub>HEX</sub>]. See Table 4.1 for command descriptions and processing time.

In CM, every command received is answered. The response consists of the two bytes of requested data or validation code, 1 byte for the check sum, and the 1-byte command reply. For more details about responses, see sections 4.3 and 4.4.

**Important:** Before sending commands that write to EEPROM registers, EEPROM programming must be enabled by sending the EEP\_WRITE\_EN command 6CF742<sub>HEX</sub>.

A read command can be sent during an active measurement cycle (i.e., the processing time has not yet elapsed after sending one of the STRT\_CYC\_x or START\_AD\_x commands indicated by gray shading in Table 4.1). For example, the SIF can be read during the START\_AD\_CNT command. If any of the other commands is to be sent during an active measurement cycle, the measurement command must first be aborted. Typically an active measurement cycle is aborted if a non-read command is received, but in special cases, the command might not be received correctly and the active measurement is not aborted. Therefore, for safe communication during an active measurement cycle, IDT recommends sending the START\_CM command [72D1<sub>HEX</sub>] first for non-read commands.

Table 4.1 Command Set

| Command<br>(HEX) | Data    | Command                                    | Notes                                                                                                                                                                                                                                                                                              | Processing<br>Time<br>@ f <sub>CLK</sub> =3MHz |

|------------------|---------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 01 / 02          |         | STRT_CYC_EEPOWI /<br>STRT_CYC_RAMOWI       | Start measurement cycle including initialization from EEPROM/RAM for digital output with activation of OWI mode OWIENA.                                                                                                                                                                            | 350μs / 220μs                                  |

| 03 / 04          |         | STRT_CYC_EEPANA /<br>STRT_CYC_RAMANA       | Start measurement cycle including initialization from EEPROM/RAM for analog output with activation of OWI mode OWIANA.                                                                                                                                                                             | 350μs / 220μs                                  |

| 05 / 06          |         | STRT_CYC_EEPOWIDIS /<br>STRT_CYC_RAMOWIDIS | Start measurement cycle including initialization from EEPROM/RAM for digital output with OWI mode disabled (OWIDIS mode).                                                                                                                                                                          | 350μs / 220μs                                  |

| 07 / 08          |         | STRT_CYC_EEP /<br>STRT_CYC_RAM †           | Start measurement cycle including initialization from EEPROM/RAM.  Note for OWIWIN and OWIANA: OWI communication is disabled after the startup window).                                                                                                                                            | 350μs / 220μs                                  |

| 10 to 1E         |         | READ_RAM                                   | Read data from RAM address 00 <sub>HEX</sub> to 0E <sub>HEX</sub> .                                                                                                                                                                                                                                | 50μs                                           |

| 30 to 43         |         | READ_EEP                                   | Read data from EEPROM address $00_{HEX}$ to $13_{HEX}$ .                                                                                                                                                                                                                                           | 50μs                                           |

| 50               |         | ADJ_OSC_ACQ                                | Acquire frequency ratio of internal oscillator to communication frequency (f <sub>OSC</sub> / f <sub>OWI</sub> ) for adjusting internal oscillator frequency by ADJREF:OSCADJ.  Important: Use this command only with OWI communication.                                                           | 50μs                                           |

| 60               | 2 Bytes | SET_DAC                                    | Set analog output (DAC) to value defined by data bytes.  Important note: If the data byte is outside the allowed range of 0100 <sub>HEX</sub> to 14FF <sub>HEX</sub> , the ZSC31150 will enter DM and output the LDR (lower diagnostic range). The AOUT pin goes into tri-state during processing. | 40μs                                           |

<sup>†</sup> Note: For product versions ZSC31150Exx and earlier, the commands STRT\_CYC\_EEP and STRT\_CYC\_RAM are not available.

| Command<br>(HEX) | Data    | Command      | Notes                                                                                                                                                                                                                                                                                                                                  | Processing<br>Time<br>@ f <sub>CLK</sub> =3MHz |

|------------------|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 62               | 2 Bytes | START_AD_CNT | Process an A/D conversion <n> (= data) times for input voltage and temperature, auto-zero corrected.  Result is updated continuously in digital output registers (4 data bytes), last values remain after processing.  See 4.5.1 for details.</n>                                                                                      | <n>* (D8+D9)<br/>commands</n>                  |

| 65               | 2 Bytes | ADJ_OSC_WRI  | Write and activate oscillator adjust value to RAM ADJREF:OSCADJ, returns compete configuration word ADJREF.  Important: Use this command only with OWI communication                                                                                                                                                                   | 50μs                                           |

| 6C               | 2 Bytes | EEP_WRITE_EN | Enable data write to EEPROM when sent with data F742 <sub>HEX</sub> ; sending any other data disables EEPROM writing.                                                                                                                                                                                                                  | 50μs                                           |

| 72               | 1 Byte  | START_CM     | Start Command Mode (CM); always send with data D1 <sub>HEX</sub> .                                                                                                                                                                                                                                                                     | 50μs                                           |

| 80 to 8E         | 2 Bytes | WRITE_RAM    | Write data to RAM addresses 00 <sub>HEX</sub> to 0E <sub>HEX</sub> respectively.                                                                                                                                                                                                                                                       | 50μs                                           |

| A0 to B2         | 2 Bytes | WRITE_EEP    | Write data to EEPROM addresses 00 <sub>HEX</sub> to 12 <sub>HEX</sub> respectively.                                                                                                                                                                                                                                                    | 12.5ms                                         |

| C0               |         | COPY_EEP2RAM | Copy the content of EEPROM addresses $00_{HEX}$ to $0E_{HEX}$ to RAM; restores EEPROM configuration in RAM.                                                                                                                                                                                                                            | 130μs                                          |

| C3               |         | COPY_RAM2EEP | Copy the content of RAM addresses $00_{HEX}$ to $0E_{HEX}$ to EEPROM; generates the EEPROM signature and writes it to address $0F_{HEX}$ , returns the EEPROM signature.                                                                                                                                                               | 200ms                                          |

| C8               |         | GET_EEP_SIGN | Calculates EEPROM signature and writes the result to SIF output register 1 (SIF1; see Table 4.2).                                                                                                                                                                                                                                      | 150μs                                          |

| C9               |         | GEN_EEP_SIGN | Calculates EEPROM signature and writes it to EEPROM address 0F <sub>HEX</sub> and writes the result to SIF1.                                                                                                                                                                                                                           | 12.6ms                                         |

| CA               |         | GET_RAM_SIGN | Calculates RAM signature and writes the result to SIF1.                                                                                                                                                                                                                                                                                | 150μs                                          |

| CF               |         | ROM_VERSION  | Get hardware and ROM version:  ROM version is defined by the low byte "CF" command answer.  Design version is defined by the high byte "CF" command answer.  ZSC31150Axx = 0Axx <sub>HEX</sub> ZSC31150Exx = 0Exx <sub>HEX</sub> ZSC31150Cxx = 0Cxx <sub>HEX</sub> ZSC31150Dxx = 0Fxx <sub>HEX</sub> ZSC31150Dxx = 19xx <sub>HEX</sub> | 50µs                                           |

Note: All Dx commands are used for the calibration process, write raw conversion result to SIF output registers, and do not generate analog output. Processing time with  $f_{CLK}$ =3MHz for D0-D6 commands is 150 clock cycles (approximately 50 $\mu$ s) + A/D conversion time. The processing time is 2 times this value for the D8 to DB commands.

Note: Enabling the A/D converter clock divider (i.e., bit CFGAFE:ADCSLOW is set to 1) doubles only the A/D conversion time.

| Command (HEX) | Command        | Notes                                                                                           |

|---------------|----------------|-------------------------------------------------------------------------------------------------|

| D0            | START_AD_BR    | Start cyclic A/D conversion at bridge sensor channel (BR); e.g., pressure measurement.          |

| D1            | START_AD_T     | Start cyclic A/D conversion at temperature channel (T).                                         |

| D2            | START_AD_SSCP  | Start cyclic A/D conversion for positive-biased Sensor Short Check and Sensor Connection Check. |

| D3            | START_AD_CMV   | Start cyclic A/D conversion for common mode voltage measurement for Sensor Aging Check.         |

| D4            | START_AD_BR_AZ | Start cyclic A/D conversion auto-zero (AZ) at bridge sensor channel (BR); e.g., pressure        |

| D5            | START_AD_TAZ   | Start cyclic A/D conversion auto-zero at temperature channel (TAZ).                             |

| Command (HEX) | Command            | Notes                                                                                                         |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------|--|

| D6            | START_AD_SSCN      | Start cyclic A/D conversion for negative-biased Sensor Short Check and Sensor Connection Check.               |  |

| D8            | START_AD_BR_AZC    | Start cyclic A/D conversion at bridge sensor channel (BR) including auto-zero.                                |  |

| D9            | START_AD_T_AZC     | Start cyclic A/D conversion at temperature channel (T) including auto-zero.                                   |  |

| DA            | START_AD_SSCP-SSCN | Start cyclic A/D conversion for positive and negative biased Sensor Short Check and Sensor Connection Check.  |  |

| DB            | START_AD_CMV_AZC   | Start cyclic A/D conversion for common mode voltage measurement (for Sensor Aging Check) including auto-zero. |  |

# 4.2. Command Processing

All commands are available for both I<sup>2</sup>C and OWI protocols (except ADJ\_OSC\_ACQ and ADJ\_OSC\_WRI). If CM is active, reception of a valid command interrupts the internal microcontroller (CMC) and starts a routine processing the received command. The processing time depends on the internal system clock frequency (minimum: ~2MHz; adjustable by EEPROM programming). For a data read from the ZSC31150, the requested data (e.g., register content or acquired measurements) is written to the SIF output register and can be read out by a read request.

Commands sent while a previously sent command has not yet executed completely will be ignored. The ZSC31150 releases the interface while a running and valid  $I^2C^{TM}$  communication takes place (i.e., a start condition of an  $I^2C^{TM}$  communication has already occurred). If the ZSC31150 does not detect a start condition, it will not provide the ACK to the address byte.

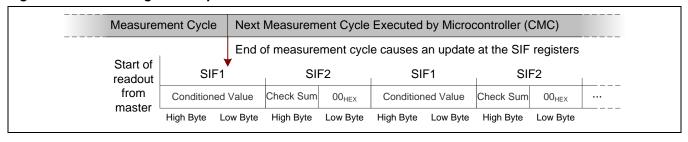

# 4.3. SIF Output Registers

The serial interface (SIF) contains two 16-bit output registers that can be read out by a read request. Depending on the configuration of ADJREF:IFOWIM, access to the one-wire interface (OWI) can be limited during NOM. Depending on the present operation mode of ZSC31150 (NOM, CM or DM; refer to section 1.3), different data are written to SIF output registers. The output registers SIF1 and SIF2 are continuously updated.

**Note:** If the update rate is high, a check sum error might occur if data is read out in NOM during an active measurement cycle or during CM for all calibration commands (e.g., the START\_AD\_CNT command). Refer to the *ZSC31150 Data Sheet* and the *ZSC31150 Bandwidth Calculation Spreadsheet* for more details about the update rate. The data readout occurs word-by-word. Therefore it is possible that during reading the first word (SIF1), the output register is updated with a new conditioned value and thus the check sum is also updated. The check sum value for the new conditioned value is read out within the next word (SIF2). The new conditioned value could have a different check sum value than was read out as the first word and so an apparent check sum error is detected.

**Recommendation:** To prevent such misinterpretation in these cases, read at least 6 bytes as shown below in Figure 4.1. If an invalid check sum is detected in the first four bytes, the second SIF1 reading can be used to check whether a misinterpretation of the check sum has occurred or a check sum error occurred. The reading of the 6 bytes must be faster than the update rate of the measurand data at SIF1.

Figure 4.1 Preventing Misinterpretation of Check Sum

Table 4.2 Output Register Contents of Serial Digital Interface (SIF) When Processing Commands

| Mode/ Commands                                                                                                 | Output Register 1 (SIF1)          |                                        | Outpu                          | Output Register 2 (SIF2) |  |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------|--------------------------------|--------------------------|--|

| wode/ Commands                                                                                                 | High Byte                         | Low Byte                               | High Byte                      | Low Byte                 |  |

| Normal Operation Mode (NOM)                                                                                    |                                   |                                        |                                |                          |  |

|                                                                                                                | Conditioned value                 |                                        | Check sum                      | 00 <sub>HEX</sub>        |  |

| Command Mode (CM)                                                                                              |                                   |                                        | ·                              |                          |  |