Nieuws

Een blik vanaf de RISC-V Summit

Er waren twee aankondigingen van IAR Systems ter ondersteuning van het opzetten van een robuust ecosysteem voor RISC-V. De eerste was met IP-provider, SiFive, om samen te werken om de compiler- en debugger-tools van de eerste naar de configureerbare processor-core IP te brengen.

Integratie van tools en IP zal ontwikkelaars ondersteunen om producten te leveren en de inzet van de open, gratis instructiesetarchitectuur (ISA) te vergroten.

Anders Holmberg, Chief Strategy Officer van IAR Systems, zei dat het doel is om ontwikkelaars te helpen de productiviteit te verhogen en zich op innovatie te concentreren. "SiFive is een leider in commerciële RISC-V core IP, en onze toolchain IAR Embedded Workbench is de meest gebruikte toolchain voor het bouwen van embedded applicaties", zei hij. Het accent ligt op schaalbare, efficiënte aangepaste silicium- en ontwikkeltools om te voldoen aan rekenwerklasten.

IAR Embedded Workbench voor RISC-V zal medio 2019 beschikbaar zijn. De toolchain beweert "toonaangevende codekwaliteit, -grootte en -snelheid" te bieden, evenals een geïntegreerde debugger met simulator- en hardware-debugondersteuning.

Het softwarebedrijf kondigde ook een samenwerking aan met de CPU IP-provider, Andes, om de RISC-V-kernen van het bedrijf, de AndesCore N25 (F) / NX25 (F) en A25 / AX25, te ondersteunen in IAR Embedded Workbench voor RISC-V. De eerste versie is medio 2019 beschikbaar. AndeStar V5 instructie-extensie en Andes Custom Extension (ACE) instructie-aanpassingsmogelijkheden zullen worden gekoppeld aan Workbench om de codesnelheid te maximaliseren en de codegrootte voor RISC-V-kernen te minimaliseren.

Automatisering en realtime computing

De nieuwste versie van de tool suite en een nieuwe EOSC-V-kern geoptimaliseerd voor Linux en real-time computing werden aangekondigd door Codasip.

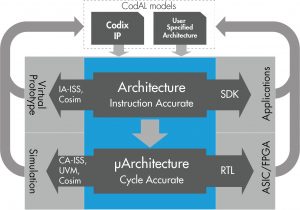

Met de Studio 8 tool suite kunnen ontwikkelaars een beschrijving op hoog niveau van een processor schrijven en het ontwerp automatisch synthetiseren (afgebeeld).

"Naarmate de RISC-V ISA-specificatie evolueert en een steeds toenemend aantal optionele architectuuruitbreidingen toevoegt, wordt een methodologie voor processorontwerp die zowel snelle architectonische verkenning als vereenvoudigde creatie van gemakkelijk implementeerbare RTL mogelijk maakt," aldus Chris Jones, Vice President van Marketing bij Codasip. "Wat nodig is, is een geavanceerde beschrijvingstaal voor processors die is geoptimaliseerd voor RISC-V," voegde hij eraan toe en introduceerde de tool suite.

De processorbeschrijving is geschreven in CodAL, een taal voor architectuurbeschrijving, en vervolgens worden de RTL van het ontwerp, de testbank, de virtuele platformmodellen en de ontwikkelset voor processorsoftware (C / C ++ compiler, debugger, profiler) automatisch samengesteld. De methodologie vermindert de tijd die nodig is om een complete softwareontwikkelingskit (SDK) te onderhouden door een instructie-accuraat (IA) processormodel in CodAL to Time te gebruiken dat anders nodig zou zijn om een volledige SDK te onderhouden en de implementatie wordt aanzienlijk verminderd dankzij de methodologie die gebruikt een instructie nauwkeurig (IA) processormodel in CodAL voor SDK generatie en een cyclus nauwkeurig model voor implementatie.

Nieuwe functionaliteit en functies voor de achtste generatie tool suite omvatten ondersteuning voor een LLVM debugger en OpenOCB, Studio / CodeSpace geïntegreerde ontwikkelomgevingen (IDE's) op basis van Eclipse Oxygen en meer interactieve consoles en verbeteringen aan de testsuites en verificatie ter ondersteuning van door de gebruiker gedefinieerde RISC -V extensies.

Het bedrijf introduceerde ook de 64-bits Bk7-processor, waarmee de familie Bk werd uitgebreid. Het heeft een zeven-fasenpijplijn met vertakkingsvoorspelling, optionele full memory management unit (MMU) met virtuele adresseringsondersteuning voor besturingssystemen zoals Linux, populaire RISC-V-standaarduitbreidingen en industriestandaard externe interfaces.

Het is de krachtigste processor van het bedrijf tot nu toe en kan door ontwikkelaars worden aangepast om instructies, registers of interfaces toe te voegen.

Studio 8 en de Bk7-processor zullen in het eerste kwartaal van 2019 algemeen beschikbaar zijn, met vroege toegang tot geselecteerde klanten onmiddellijk.

Microchip heeft aangekondigd dat het naar eigen zeggen de eerste RISC-V SoC FPGA-architectuur in de branche aan haar Mi-V-ecosysteem toevoegt. De FPGA's combineren Microsemiconductor PolarFire FPGA's en een microprocessorsubsysteem gebaseerd op de RISC-V ISA.

Voorafgaand aan de Summit kondigde de Linux Foundation haar samenwerking met de RISC-V Foundation aan om de open source-ontwikkeling en de adoptie van de RISC-V ISA te versnellen.