Message

Une vue du Sommet RISC-V

Il y a eu deux annonces de IAR Systems en faveur de l'établissement d'un écosystème robuste pour RISC-V. La première a été avec le fournisseur IP, SiFive, de collaborer pour apporter les premiers outils de compilateur et de débogueur au noyau IP du processeur configurable.

L'intégration d'outils et d'IP devrait aider les développeurs à fournir des produits et à accroître le déploiement de l'architecture ouverte et gratuite d'instructions (ISA).

Anders Holmberg, directeur de la stratégie chez IAR Systems, a déclaré que l'objectif était d'aider les développeurs à augmenter leur productivité et à se concentrer sur l'innovation. «SiFive est un leader dans le domaine IP commercial RISC-V, et notre chaîne d'outils IAR Embedded Workbench est la chaîne d'outils la plus largement utilisée pour créer des applications intégrées», a-t-il déclaré. L'accent est mis sur des outils de développement et de silicium personnalisés évolutifs et efficaces pour répondre aux charges de travail de calcul.

IAR Embedded Workbench pour RISC-V sera disponible mi-2019. La chaîne d'outils prétend offrir «la meilleure qualité, taille et vitesse de code» ainsi qu'un débogueur intégré avec prise en charge du débogage du simulateur et du matériel.

La société de logiciels a également annoncé un partenariat avec le fournisseur d'IP CPU, Andes, pour prendre en charge les cœurs RISC-V de l'entreprise, les AndesCore N25 (F) / NX25 (F) et A25 / AX25, dans IAR Embedded Workbench pour RISC-V. La première version sera disponible mi-2019. L'extension d'instruction AndeStar V5 et les capacités de personnalisation de l'instruction Andes Custom Extension (ACE) seront couplées à Workbench pour maximiser la vitesse du code et minimiser la taille du code pour les cœurs RISC-V.

Automatisation et informatique en temps réel

Codasip a annoncé la dernière version de sa suite d'outils et un nouveau cœur EOSC-V optimisé pour Linux et l'informatique en temps réel.

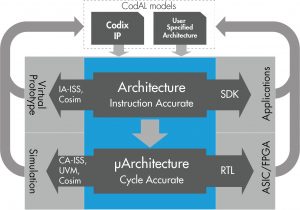

Sa suite d'outils Studio 8 permet aux développeurs d'écrire une description de haut niveau d'un processeur et synthétise automatiquement la conception (photo).

«Alors que la spécification RISC-V ISA évolue et ajoute un nombre toujours croissant d'extensions d'architecture en option, une méthodologie de conception de processeur qui permet à la fois une exploration architecturale rapide et une création simplifiée de RTL facilement implémentable devient essentielle», a observé Chris Jones, vice-président de Marketing chez Codasip. «Ce dont nous avons besoin, c'est d'un langage de description de processeur de haut niveau optimisé pour RISC-V», a-t-il ajouté en présentant la suite d'outils.

La description du processeur est écrite en CodAL, un langage de description d’architecture, puis la RTL, le banc de test, les modèles de plate-forme virtuelle et le kit de développement logiciel du processeur (compilateur C / C ++, débogueur, profileur) sont automatiquement synthétisés. La méthodologie réduit le temps passé à maintenir un kit de développement logiciel complet (SDK) en utilisant un modèle de processeur précis (IA) dans CodAL to Time qui serait autrement nécessaire pour maintenir un SDK complet et la mise en œuvre est considérablement réduite grâce à la méthodologie qui utilise un modèle de processeur précis d'instructions (IA) dans CodAL pour la génération de SDK et un modèle précis de cycle pour la mise en œuvre.

Les nouvelles fonctionnalités et fonctionnalités de la suite d'outils de huitième génération incluent la prise en charge d'un débogueur LLVM et OpenOCB, des environnements de développement intégrés (IDE) Studio / CodeSpace basés sur Eclipse Oxygen et des consoles plus interactives et des améliorations des suites de tests et de la vérification pour prendre en charge RISC défini par l'utilisateur -V extensions.

La société a également introduit le processeur 64 bits Bk7, ajoutant à la famille Bk. Il dispose d'un pipeline en sept étapes avec prédiction de branche, d'une unité de gestion de mémoire complète (MMU) en option avec prise en charge de l'adressage virtuel pour les systèmes d'exploitation tels que Linux, des extensions standard RISC-V populaires et des interfaces externes standard.

Il s'agit du processeur le plus performant de l'entreprise à ce jour et il est personnalisable pour les développeurs pour ajouter des instructions, des registres ou des interfaces.

Studio 8 et le processeur Bk7 seront généralement disponibles au premier trimestre 2019, avec un accès anticipé à certains clients immédiatement.

Microchip a annoncé qu'elle ajoutait à son écosystème Mi-V ce qu'elle considère être la première architecture FPC SoC RISC-V du secteur. Les FPGA associent des FPGA microsemi-conducteurs PolarFire et un sous-système de microprocesseur basé sur le RISC-V ISA.

Avant le Sommet, la Linux Foundation a annoncé sa collaboration avec la RISC-V Foundation pour accélérer le développement open source et l'adoption de RISC-V ISA.