Noticias

Una vista desde la Cumbre RISC-V

Hubo dos anuncios de IAR Systems en apoyo del establecimiento de un ecosistema robusto para RISC-V. El primero fue con el proveedor de IP, SiFive, para colaborar en llevar las herramientas del compilador y depurador del anterior a la IP central del procesador configurable.

Se espera que la integración de herramientas e IP ayude a los desarrolladores a entregar productos y a aumentar la implementación de la arquitectura de conjunto de instrucciones (ISA) abierta y gratuita.

Anders Holmberg, director de estrategia de IAR Systems, dijo que el objetivo es ayudar a los desarrolladores a aumentar la productividad y centrarse en la innovación. "SiFive es líder en IP comercial RISC-V y nuestra cadena de herramientas IAR Embedded Workbench es la cadena de herramientas más utilizada para construir aplicaciones integradas", dijo. El énfasis está en herramientas de desarrollo y silicio personalizadas, escalables y eficientes para cumplir con las cargas de trabajo informáticas.

IAR Embedded Workbench para RISC-V estará disponible a mediados de 2019. La cadena de herramientas afirma ofrecer "calidad, tamaño y velocidad de código líderes", así como un depurador integrado con simulador y soporte de depuración de hardware.

La compañía de software también anunció una asociación con el proveedor de CPU IP, Andes, para soportar los núcleos RISC-V de la compañía, los AndesCore N25 (F) / NX25 (F) y A25 / AX25, en IAR Embedded Workbench para RISC-V. La primera versión estará disponible a mediados de 2019. La extensión de instrucción AndeStar V5 y las capacidades de personalización de instrucción de Andes Custom Extension (ACE) se combinarán con Workbench para maximizar la velocidad del código y minimizar el tamaño del código para los núcleos RISC-V.

Automatización y computación en tiempo real.

Codasip anunció la última versión de su conjunto de herramientas y un nuevo núcleo EOSC-V optimizado para Linux y computación en tiempo real.

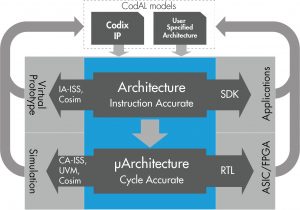

Su conjunto de herramientas Studio 8 permite a los desarrolladores escribir una descripción de alto nivel de un procesador y sintetiza automáticamente el diseño (en la foto).

"A medida que la especificación RISC-V ISA evoluciona y agrega un número cada vez mayor de extensiones de arquitectura opcionales, una metodología de diseño de procesador que permite la exploración arquitectónica rápida y la creación simplificada de RTL fácilmente implementable se vuelve esencial", observó Chris Jones, vicepresidente de Marketing en Codasip. "Lo que se necesita es un lenguaje de descripción de procesador de alto nivel optimizado para RISC-V", agregó, presentando el conjunto de herramientas.

La descripción del procesador está escrita en CodAL, un lenguaje de descripción de arquitectura, y luego el RTL del diseño, el banco de pruebas, los modelos de plataforma virtual y el kit de desarrollo de software del procesador (compilador C / C ++, depurador, generador de perfiles) se sintetizan automáticamente. La metodología reduce el tiempo dedicado a mantener un kit completo de desarrollo de software (SDK) mediante el uso de un modelo de procesador de instrucción precisa (IA) en CodAL to Time que de lo contrario sería necesario para mantener un SDK completo y la implementación se reduce significativamente gracias a la metodología que utiliza un modelo de procesador de instrucción precisa (IA) en CodAL para la generación de SDK y un modelo de ciclo preciso para la implementación.

La nueva funcionalidad y características para el conjunto de herramientas de octava generación incluyen soporte para un depurador LLVM y OpenOCB, entornos de desarrollo integrado (IDE) Studio / CodeSpace basados en Eclipse Oxygen y más consolas interactivas y mejoras en los conjuntos de pruebas y verificación para admitir RISC definido por el usuario -V extensiones.

La compañía también presentó el procesador Bk7 de 64 bits, que se sumó a la familia Bk. Tiene una tubería de siete etapas con predicción de rama, unidad de administración de memoria completa (MMU) opcional con soporte de direccionamiento virtual para sistemas operativos como Linux, extensiones estándar RISC-V populares e interfaces externas estándar de la industria.

Es el procesador de más alto rendimiento de la compañía hasta la fecha y es personalizable para que los desarrolladores agreguen instrucciones, registros o interfaces.

Studio 8 y el procesador Bk7 estarán generalmente disponibles el primer trimestre de 2019, con acceso anticipado a clientes seleccionados de inmediato.

Microchip anunció que está agregando lo que cree que es la primera arquitectura FPGA SoC RISC-V de la industria a su ecosistema Mi-V. Los FPGA combinan los FPGA Microsemiconductor PolarFire y un subsistema de microprocesador basado en el RISC-V ISA.

Antes de la Cumbre, la Fundación Linux anunció su colaboración con la Fundación RISC-V para acelerar el desarrollo de código abierto y la adopción de la ISA RISC-V.