Nyheder

Udsigt fra RISC-V-topmødet

Der var to meddelelser fra IAR Systems til støtte for etablering af et robust økosystem for RISC-V. Den første var med IP-udbyder, SiFive, for at samarbejde om at bringe førstnævnte compiler- og debugger-værktøjer til den konfigurerbare processor-IP.

Integration af værktøjer og IP forventes at støtte udviklere til at levere produkter og øge implementeringen af den åbne, gratis instruktionssætarkitektur (ISA).

Anders Holmberg, Chief Strategy Officer, IAR Systems, sagde, at målet er at hjælpe udviklere med at øge produktiviteten og fokusere på innovation. "SiFive er førende inden for kommerciel RISC-V core IP, og vores værktøjskæde IAR Embedded Workbench er den mest anvendte værktøjskæde til opbygning af indlejrede applikationer," sagde han. Accenten er på skalerbar, effektiv tilpasset silicium og udviklingsværktøjer til at imødegå beregne arbejdsmængder.

IAR Embedded Workbench til RISC-V vil være tilgængelig medio 2019. Værktøjskæden hævder at tilbyde "førende kodekvalitet, størrelse og hastighed" samt en integreret debugger med support til simulator og hardware.

Softwarevirksomheden annoncerede også et partnerskab med CPU IP-udbyderen, Andes, til støtte for virksomhedens RISC-V-kerner, AndesCore N25 (F) / NX25 (F) og A25 / AX25, i IAR Embedded Workbench til RISC-V. Den første version vil være tilgængelig i midten af 2019. AndeStar V5-instruktionsudvidelse og ACE-instruktionstilpasningsfunktioner for Andes Custom Extension vil blive koblet med Workbench for at maksimere kodehastighed og minimere kodestørrelse for RISC-V-kerner.

Automation og realtids computing

Den nyeste version af sin værktøjssuite og en ny EOSC-V-kerne, der er optimeret til Linux og realtids computing, blev annonceret af Codasip.

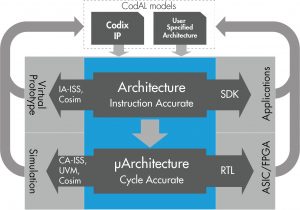

Dens Studio 8-værktøjssuite giver udviklere mulighed for at skrive en beskrivelse på højt niveau af en processor og syntetiserer automatisk designet (på billedet).

"Efterhånden som RISC-V ISA-specifikationen udvikler sig og tilføjer et stadigt stigende antal valgfri arkitekturudvidelser, bliver en processor-designmetodologi, der muliggør både hurtig arkitektonisk efterforskning og forenklet oprettelse af let implementerbar RTL," observerede Chris Jones, vicepræsident for Marketing hos Codasip. ”Det, der kræves, er et højt-niveau-processor-sprog, der er optimeret til RISC-V,” tilføjede han og introducerede værktøjssuite.

Processorbeskrivelsen er skrevet i CodAL, et arkitekturbeskrivelsessprog, hvorefter designets RTL, testbænk, virtuelle platformmodeller og processorsoftwareudviklingssæt (C / C ++ compiler, debugger, profiler) syntetiseres automatisk. Metodologien reducerer tidsforbruget ved at opretholde et komplet softwareudviklingssæt (SDK) ved at bruge en instruktionsnøjagtig (IA) -processormodel i CodAL til tid, som ellers ville være påkrævet for at opretholde en komplet SDK, og implementeringen reduceres markant takket være den metode, der bruger en instruktionsnøjagtig (IA) processormodel i CodAL til SDK-generation og en cyklusnøjagtig model til implementering.

Ny funktionalitet og funktioner til den ottende generation af værktøjssæt inkluderer support til en LLVM-debugger og OpenOCB, Studio / CodeSpace integrerede udviklingsmiljøer (IDE'er) baseret på Eclipse Oxygen og flere interaktive konsoller og forbedringer af testsuiterne og verificeringen for at understøtte brugerdefineret RISC -V udvidelser.

Virksomheden introducerede også den 64-bit Bk7-processor, hvilket tilføjede Bk-familien. Det har en syv-trins pipeline med brancheforudsigelse, valgfri fuld hukommelsesadministrationsenhed (MMU) med virtuel adresseringssupport til operativsystemer som Linux, populære RISC-V standardudvidelser og eksterne standardgrænseflader til industrien.

Det er selskabets hittil mest effektive processor og kan tilpasses for udviklere at tilføje instruktioner, registre eller grænseflader.

Studio 8 og Bk7-processoren vil være generelt tilgængelig Q1 2019 med hurtig adgang til udvalgte kunder med det samme.

Microchip annoncerede, at den tilføjede, hvad den mener at være branchens første RISC-V SoC FPGA-arkitektur til sit Mi-V-økosystem. FPGA'erne kombinerer Microsemiconductor PolarFire FPGA'er og et mikroprocessorundersystem baseret på RISC-V ISA.

I forkant af topmødet annoncerede Linux Foundation sit samarbejde med RISC-V Foundation for at fremskynde open source-udvikling og vedtagelse af RISC-V ISA.